What is a Processor

Processor is programmable electronic circuitry that performs operations according to the instructions stored in memory. The processor as of itself does not have the memory and I/O devices. The processor reads the instructions stored in the memory, interprets it, and stores the output in memory or signals the I/Os. Processor Consists of the Processor core which contains circuitry for instruction fetching, decoding, and execution, register banks, and control units.

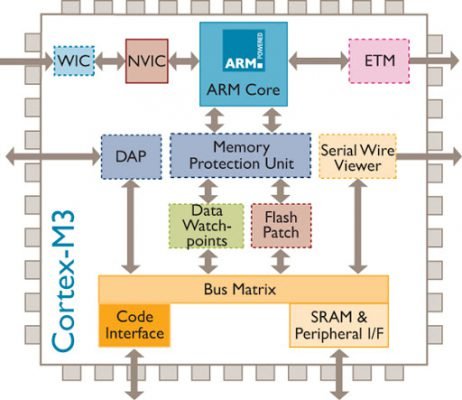

According to the architecture design of the processor, the different processors have different components. For example, ARM cortex-M4 processors have NVIC, MPU, Floating point units, optional debug subsystems.

Fig 1.1 – Block Diagram of the Cortex-M3 and Cortex-M4 Processor.

The processor is the part of the Microcontroller and not a microcontroller as a whole and it takes only a small part of the silicon area. Processor design companies design the processors and various components that silicon designers need and license these designs to various silicon design companies including microcontroller vendors. These designs are called Intellectual Property (IP) and the business model is called IP licensing. Although many microcontroller vendors use ARM processors as their choice of CPU, the memory system, memory map, memory size, and peripherals can be completely different from one product to another.

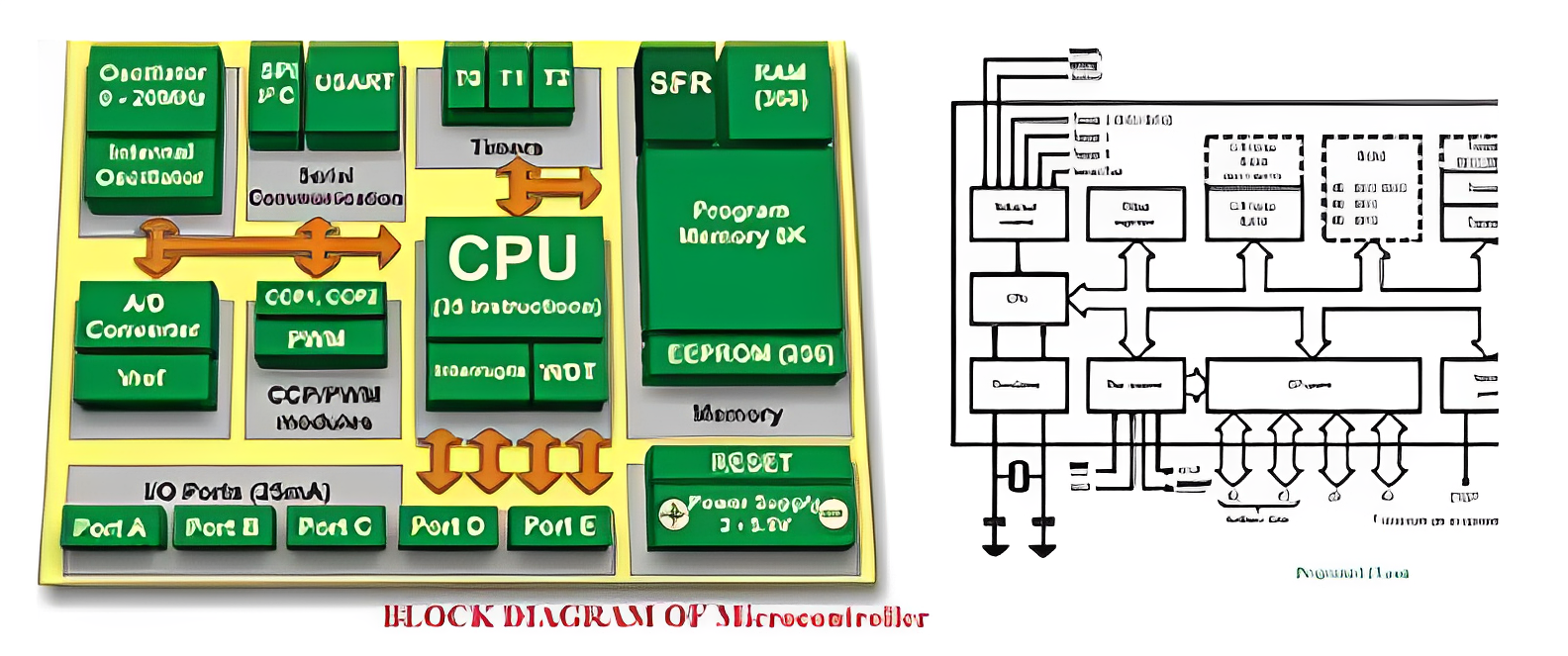

This allows the microcontroller vendors to design differently. A block diagram of the microcontroller.

Fig 1.2 – A microcontroller contains Many different blocks

How does Processor control the world?

Processors become an integral part of our life. We come across many devices which have processors embedded in them. For example:

- The smartphone on which I am writing this article has ARM cortex-A55 and cortex-A75 as processor,

- The Famous Tesla motors FSD Self-driving computer has many ARM processors.

To give the idea of how processors are running the world look at these two examples.

- Upto 2019, Arm partners have shipped more than 160 billion Arm-based chips.

- Due to the shortage of semiconductor chips(processors) many car manufacturing companies had to reduce the number of cars manufactured.

ARM Processor

ARM processors are designed by ARM Ltd., ARM does not manufacture processors or sell the chips directly. Instead ARM licenses these designs to other semiconductor companies so that they can make their processor, microcontroller, SOCs as ARM processors are configurable. In the Cortex processor range, the processors are divided into three profiles:

1) The A Profile is designed to handle complex applications such as high-end embedded OSs.

2) The R profile processors are targeted primarily at the high end of the real-time market. These are applications, such as hard drive controllers, automotive systems, etc.

3) The M profile processors target smaller-scale applications such as microcontrollers and mixed-signal design.

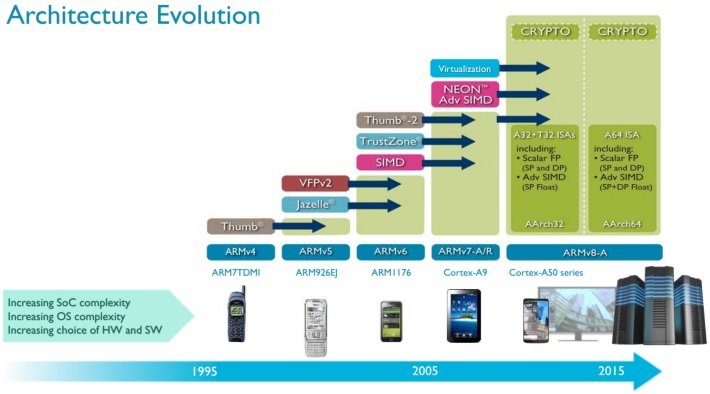

ARM develops new processors, new instructions, and architectural features are added from time to time, as a result, there are different versions of the architecture. For example:

- ARM7TDMI is based on the architecture version ARMv4T.

- ARMv5TE architecture was introduced with the ARM9E processor families.

- With the ARM11 Processor family, the architecture was extended to ARMv6 with memory system features and SIMD instructions included.

- Cortex family processors are based on ARMv7 and ARMv6.

The cortex-M3 and cortex-M4 processors are based on ARMv7-M architecture. The architecture evolution of the ARM can be seen in the following (Fig 1.4). All the cortex-M processors support Thumb-2 technology(16-bit and 32-bit instructions), with no need to switch the processor between Thumb state and ARM state.

Figure 1.4 : Evolution of ARM

Figure 1.5

STM32 series is shown

How to ARM Processor based MCU's ?

The language used to program MCU is C/C++, but mostly C is used. There are many development suites available from open-source free tools, to budget low-cost tools, to high-end commercial, to mcu vendors propiatery IDE’s. packages. Some development toolchains are:

For Programming and debugging ARM Processor based MCU’s, we will be using Microcontrollers of different vendors like: STMicroelectronics and NXP Semiconductors.

We will be using STM32 Family of STMicroelectronics and S32 Family of NXP Semiconductors. Both of these are based on ARM Processor and have rich set of features and specifications which are ideal for learning embedded systems.

Now both the companies provide their own IDE’s for : STM32CubeIDE and S32 Design IDE for respective family of MCU mentioned above.

Or we can also use the Above-mentioned IDE’s which are general IDE’s can be used to program any ARM processor based MCU. But recomended one is to use Vendor specific IDE as it has many extra featutes for programming.

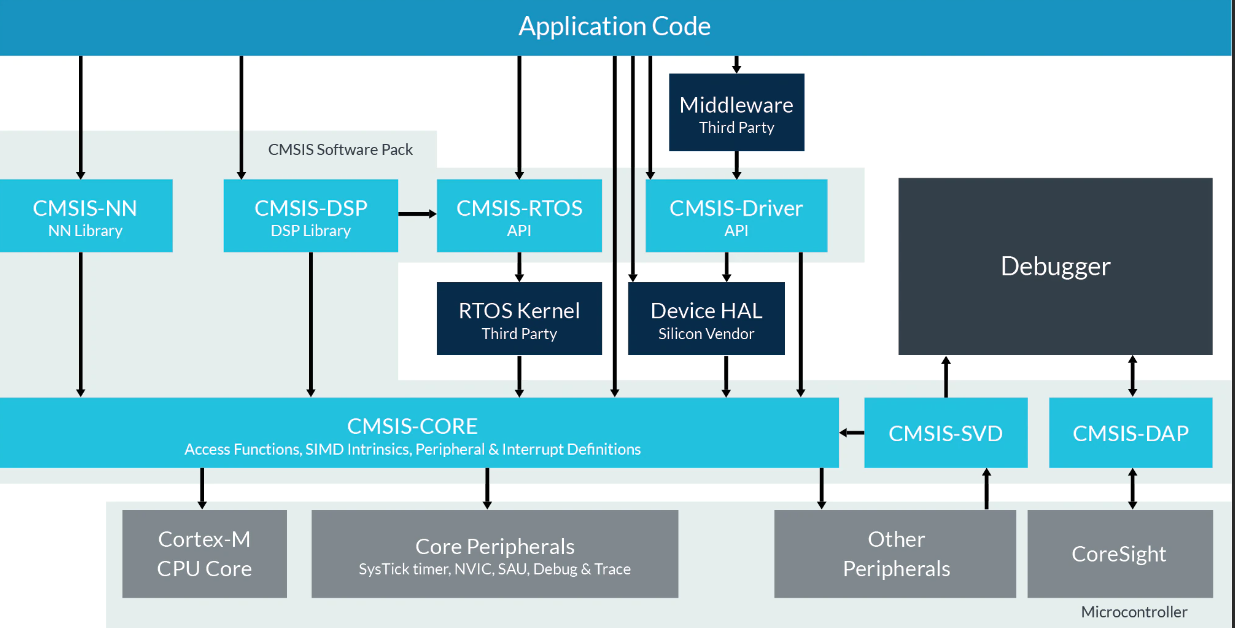

CMSIS

The Common Microcontroller Software Interface Standard(CMSIS) was developed by ARM to allow microcontroller and software vendors to use a consistent software infrastructure to develop software solutions for cortex microcontrollers.

THE AIM OF CMSIS:

- Software reusability: make it easier to reuse code with different Cortex-M processors, reducing time to market and verification efforts.

- Software compatibility: Due to consistent software infrastructure, software from various sources can work together, reducing the risk in integration.

- The CMSIS allows easy access to processor core features from the c language.

- CMSIS-compliant device drivers can be used with various compilation tools.

CMSIS started out as a way to establish consistency in device-driver for the Cortex-M microcontrollers, and this has become CMSIS-Core.

Since then, additional CMSIS projects have started:

A set of APIs for applications developers to access the features on the Cortex-M processor regardless of microcontroller devices and toolchain used.

This library is intended to allow software developers to create DSP applications on Cortex-M microcontrollers easily.

the System View Description in an XMl-based file format to describe peripheral set in microcontroller products.

the CMSIS-RTOS is an API specification for embedded OS running on Cortex-M Microcontrollers.

the CMSIS-DAP(Debug Access Port) is a reference design for a debug interface adaptor, which supports USB to JTAG/Serial protocol conversions.

The CMSIS files are integrated into device-driver library packages from the microcontroller vendor. So when you are using CMSIS-compliant device-driver libraries provided by the microcontroller vendors, you are already using CMSIS.

We can define the CMSIS into multiple layers:

Name definitions,address definitions, and helper functions to access core registers and core peripherals. This is processor specific and is provided by ARM.

Name definitions, address definitions of peripheral registers etc. This is device specific.

Access Functions For Peripherals

How do I use CMSIS-Core ?

Add Source files to the project. This includes:

- Device specific, toolchain-specific startup code, in the form of assembly or C.

- Device-specific device initialization code(e.g. System_c).

Add header files into the search path of the project:

- A device-specific header file for peripheral registers definitions and interrupt assignment definitions(e.g., .h)

- A device-specific header file for functions in device initialization code(e.g, system_.)

- A number of processor-specific header files(e.g, corre_cm3.h,core_cm4.h)

- Optionally additional vendor-specific header files for peripheral access functions.

The IDE automatically sets up the startup code for you when you create a new project. Otherwise, you just need to add the startup code from the device-driver library to the project manually. Startup code is required for the starting sequence of the processor, and it also includes the exception vector table definition that is required for interrupt handling.

STM32 HAL is an abstract lawyer ensuring minimized portability across the STM32 Portfolio. HAL APIs are available for all peripherals. These hide the MCU and peripheral complexity from the end-user.

Low-Layer APIs(LL) offer a fast lightweight layer that is closer to the hardware than the HAL. LL APIs are available only for a set of peripherals. These require deep knowledge of the MCU and peripheral specifications.

CONCLUSION PARAGRAPH: In this article, we just scratched the surface of the embedded world. In the upcoming articles, we will learn embedded development by doing projects.

Next Blog To Read for STM32

GPIO Peripheral in STM32F103 MCU

Table of Contents GPIO Theory So now we’ll talk about GPIO pins . GPIO stands for general purpose input output

STM32F103 & ADC: Single Channel Conversion

In the last post, we have gotten to know about the features of ADC Peripheral that we have in STM32

PWM on STM32F103

What is PWM? PWM or Pulse Width Modulation, is a type of digital electrical signal which is periodic in nature,

Blogs to read for ARM Processor

Light Beige Sleek and Simple Blogger Personal Website by KsmaVideoEditor harsh gettobyte technp;pgies

Getting Hands-On with NXP eIQ: A “No Code” Starter Guide for Edge AI Developers

Introduction In a world driven by AI and IoT, deploying machine learning at the edge has become essential. NXP’s eIQ™

FRDM i.MX93 Demystified: The Hardware That Makes AI Work at the Edge

Imagine you’re handed a powerful little board, no bigger than your palm. At first glance, it looks like a jungle

How to Run AI on a Microcontroller or Microprocessor – A Beginner’s Guide to Edge AI

In the last few years, Edge AI has rapidly transformed how devices understand and interact with the world — without

Edge AI ToolKit: EiQ AI SDK

Introduction to EiQ In previous blogs, we’ve discussed in depth Edge AI, its features, advantages, and future scopes. Implementation of