Introduction

–> Welcome everyone, today’s topic of discussion is the ADC Peripheral in S32K144. ADC(Analog-to-Digital Converter) Peripheral enables the microcontroller to convert the analog signal into digital form which can be utilized by the microcontroller for different purposes. For brief ADC understanding as a concept, redirect yourself to this BLOG. But for those who want to learn good enough knowledge, they can stick to this blog. Now, the first question after knowing “what is ADC”, everyone may think “Why ADC?”. To answer this “why”, you just look around yourself, and you may notice 82% of the signal are analogous in nature. Let’s take some examples to clarify this 82% fact, firstly the power you are using to glow light, fan, or room conditioner in the room is analog in nature called a sinusoidal wave, secondly, the music we hear in our daily life also an analog signal and many more. To understand these signals, microcontrollers need digitalization of these analog values with a reference scale which Is provided by ADC peripheral. There are major technical concepts and terminology to be learned which will be represented in a complete blog. First, Sampling which converts the continuous signal into a series of discrete values. Second, Quantization helps in converting the discrete samples into digital values. At last, Resolution resembles the precision of the digital representation, you can consider this as More Resolution means Reading with more decimals(accuracy). This is more than sufficient theory for begging with ADC Peripheral. let’s move towards practical learning and see the features offered by S32K144 for ADC.

Features of ADC

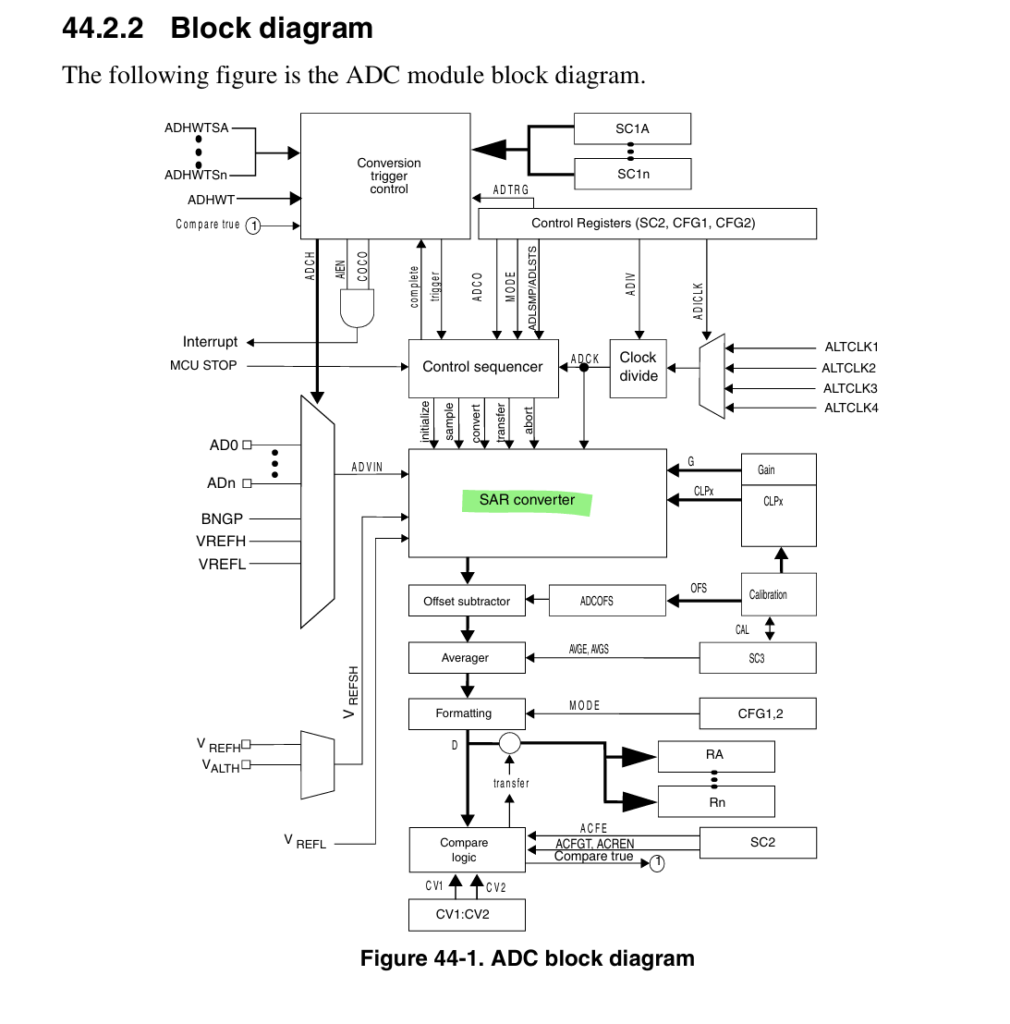

> SAR ADC

- The very first feature of ADC is its type, which is SAR(Successive Approximation Register) ADC(Analog-to-Digital Convertor). Those who are in-depth learners, can refer to this BLOG which describes the SAR in ADC, and compare it with other types. In a gist, I tell you, that SAR ADC is the perfect balance of speed, accuracy, and power efficiency compared to other ADC types.

- As According to block diagram of ADC in S32K144, its has SAR type ADC converter.

> ADC Instances and ADC pins in S32K1xx MCU’s

- ADC Peripheral offered by S32K144 consists of two 12-bit ADC modules, ADC0 and ADC1. Each module contains 16 single-ended analog input channels. Both of these modules can be used individually as well as combined(called interleaved functionality, we’ll be discussing further section).

> Single-ended 12-bit, 10-bit, and 8-bit Output Modes

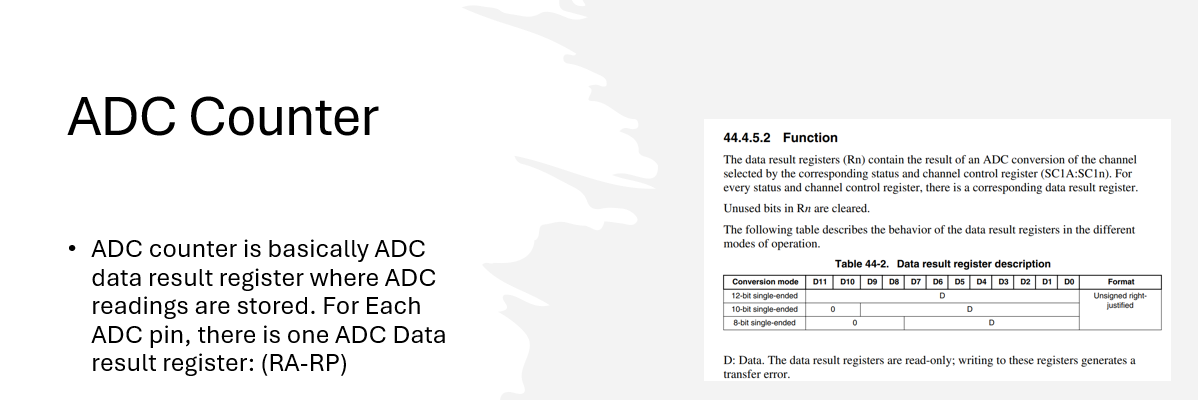

- ADC counter is basically ADC data result register where ADC readings are stored. For Each ADC pin, there is one ADC Data result register: (RA-RP).

- ADC counter value is selected via MODE bits of ADC CFG1 register.

ADC Data Result Register - These output modes resemble the Resolution of ADC.

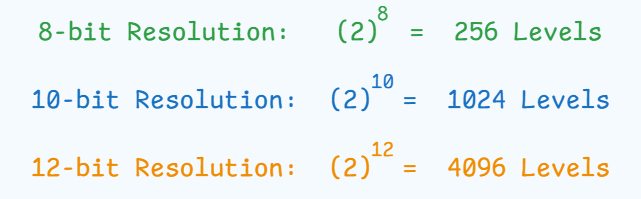

- Let’s break down how precision increases with an increase in resolution. 8-bit resembles that 2 raise to the power 8 = 256 which means only in 256 distinct levels an analog signal can be sliced. Similarly for 10-bit resolution, 10-bit resembles that 2 raise to the power 10 = 1024 which means only in 1024 distinct levels an analog signal can be sliced. Also same goes for 12-bit resolution, the number of distinct levels is 4096 = 2 raising to the power 12.

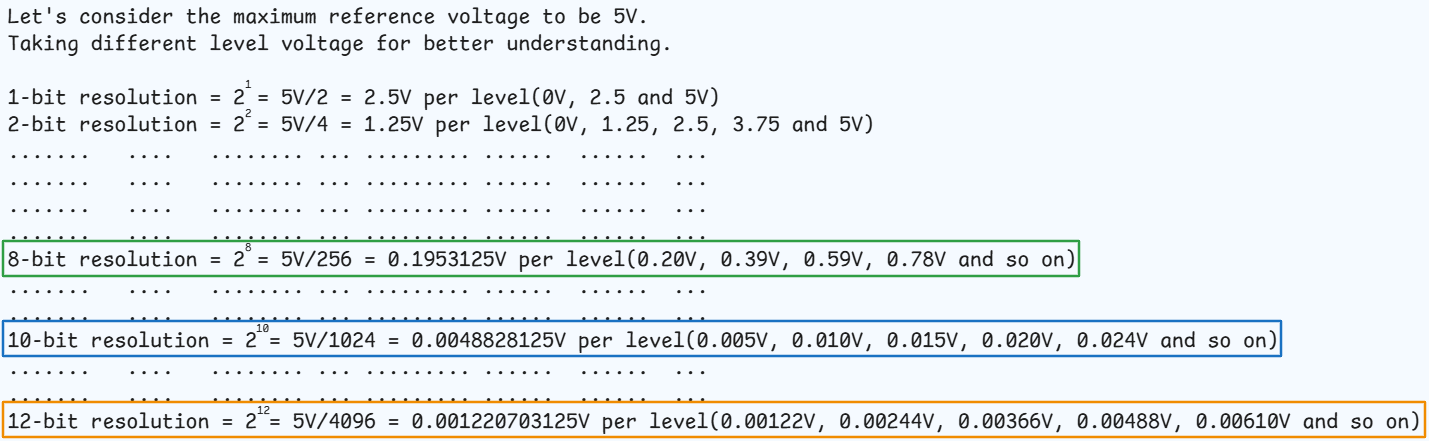

- Let’s say that we are taking reference of 5V for ADC conversion, reference creates a band of operating range where an Amplitude of 5V is the maximum analog input that can converted by ADC and an amplitude greater than 5V will only show the maximum reference value. You can change the reference for the ADC as per the microcontroller specification mentioned in the datasheet.

- Coming back to our 5V reference, now for this reference we can also calculate the precision level of resolution. if we choose 8-bit resolution with 5V reference, then we can convert the discrete level in voltage, that is 5V/256 = 0.01953125V (~19.53mV) per level. Similarly, for a 10-bit resolution, this value will be (~4.88mV per level), and for a 12-bit resolution, it is (~1.22mV per level). By investing formula only you can calculate different levels for different voltages.

> Single or Continuous Conversion Modes

By means of conversion modes, we understand which type of conversion we want whether it should be continuous in nature or one at a time.

- Let’s assume you have a condition where you want to convert analog to digital signal consistently and check whether it surpasses the threshold value or not. In this specific condition, you fastest conversion without any delay, this condition can be fulfilled with the Continuous Conversion Mode of ADC where you have to start the ADC once then the conversion will automatically take place at the speed of the ADC clock input(which can be varied).

- To understand the Single Conversion Mode, let’s consider another condition where you have to read the analog value at a specific time interval(like every 2 min or 5 min) where the threshold comparing is a period in time. Then you assign this role to some other peripheral, which calculates this time period for you and then invokes a request to ADC peripheral for conversion. These require the Single Conversion Mode of ADC peripheral where conversion needs to take place only when needed.

As we talked about the linking between the other peripheral and ADC peripheral is done by Trigger MUX and PDB module (which are further topics of discussion).

> Automatic Return to IDLE after a Single Conversion

- This is one of the most important which can create a big mess in operating the ADC peripheral and extracting the results.

- Firstly, the most important thing to thing to understand in the above-mentioned feature is that Single Conversion here doesn’t mean conversion mode, it is written as a statement without any technical reference. Single conversion means state after one conversion is completed.

- Secondly, This Feature wants to mention that after a conversion is completed, the result is placed in the Rn data registers. The respective SC1n[COCO] is then set, after this bit is set, no new conversion will be done until an SC1n[COCO] is cleared. This COCO bit automatically clears when you read the result of ADC conversion using software API. If the COCO bit is not cleared, the ADC peripheral will remain IDLE until the COCO bit is cleared. And this is also not a one-time feature, it follows every time in any conversion.

> Configurable Sample Time and Conversion Speed/Power

- First, regarding power control, the ADC module stays in its idle state until a conversion is triggered. In this state, the ADC conversion process is effectively held in reset.

- Now, it is time to understand Configurable Sample Time, Before going to Configurable Sample Time, we need to know about Sample Time, Sample Time is the number of ADC Clock Cycles for which input samples are taken. To understand this clock cycle, let’s take a simple example and understand it. consider a clock with a frequency of 1KHz then calculate its one-clock cycle time, you just have to reciprocate the frequency, in our case, which will be 1/1000Hz = 1ms which means a single ADCK clock cycle is 1ms. Range of Configurable Sample Time is 1-255. Now you get the understanding of how Configurable Sample TIme works, in our condition if I use 255(Maximum value of Configurable Sample Time) then for 255 ADCKclock cycle = 255 ms meaning one single ADC conversion is done by sampling the analog signal for 255ms.

- The last remaining is Conversion Speed or Total Conversion Time, The parameters on which Conversion Time depends are:

- The sample time as determined by CFG2[SMPLTS]

- The MCU bus frequency

- The conversion mode, as determined by CFG1[MODE]

- The frequency of the conversion clock, that is, fADCK.

- After the module becomes active, sampling of the input begins.

- CFG2[SMPLTS] selects between sample times based on the selected conversion mode.

- When sampling is completed, the converter is isolated from the input channel, and a successive approximation algorithm is applied to determine the digital value of the analog signal.

- The result of the conversion is transferred to Rn upon completion of the conversion algorithm.

- The maximum total conversion time is determined by the clock source chosen and the divide ratio selected. The clock source is selectable by CFG1[ADICLK], and the divide ratio is specified by CFG1[ADIV]. To calculate total conversion time the following formula is applied:

ADC TOTAL CONVERSION TIME = Sample Phase Time (set by SMPLTS + 1) + Hold Phase (1 ADC Cycle) + Compare Phase Time (8-bit Mode = 20 ADC Cycles, 10-bit Mode = 24 ADC Cycles, 12-bit Mode = 28 ADC Cycles) + Single or First continuous time adder (5 ADC cycles + 5 bus clock cycles)

> Conversion Complete(COCO) and Hardware Average(AVGE) Complete Flag

- As we discussed above, one of the functions, the COCO flag or Conversion Complete flag, indicates the completion of ADC conversion. Now we also have to see how Conversion Completion happens and store the results in the Data Register with its dependency on Comparing Function or Hardware Averaging or both.

- An interrupt is generated if the respective SC1n[AIEN] is high at the time that the respective SC1n[COCO] is set.

- Now understand Hardware Averaging. Hardware Averaging as it is very much self-explanatory terminology where this function provides averaging of samples. This is specifically called HARDWARE averaging because we as a firmware developer don’t do any kind of development on the software end for averaging. The hardware average function can be enabled by setting SC3[AVGE] = 1 to perform a hardware average of multiple conversions. The number of conversions is determined by the AVGS[1:0] bits, which can select 4, 8, 16, or 32 conversions to be averaged. While the hardware average function is in progress, SC2[ADACT] will be set. After the chosen input is sampled and converted, the result is stored in an accumulator. Once the specified number of conversions is completed, an average is calculated. With hardware averaging enabled, a single conversion completion does not set the SC1n[COCO] flag. If the compare function is disabled or returns true, the average result is transferred to the data result registers, Rn, and SC1n[COCO] is set once the selected number of conversions are finished. If ADC interrupts are enabled (SC1n[AIEN] = 1), an interrupt is generated when SC1n[COCO] is set.

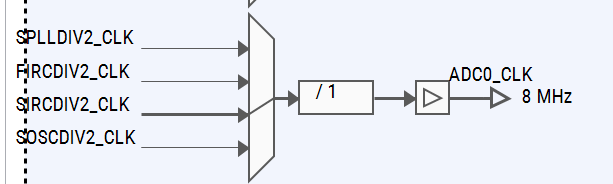

> Input Clock Selectable (from up to four sources)

- ADCK Clock is not an independent clock in the MCU. It is connected through MCU’s main clock option and then it runs on the very same frequency.

- But we can always customize the clock period of ADC peripheral by choosing a different clock and prescalar. Prescalar is a specific value that divides the clock into desired frequencies,

ADC Clock in S32K144 - Four available clock sources are mentioned below, but to learn about these clocks deeply you can refer clock peripheral blog.

- FIRC: Fast Internal RC (Resistor-Capacitor) Oscillator

- SIRC: Slow Internal RC (Resistor-Capacitor) Oscillator

- SPLL: System Phase-Locked Loop

- SOSC: System OSCillator

- Clock selection is managed by setting the CFG1[ADICLK] register.

- Regardless of the selected clock, its frequency must stay within the specified range for ADCK(2MHz-50MHz). If the available clock speed is too low, the ADC may not meet performance specifications. Conversely, if the clock is too fast, it must be divided to fall within the required frequency range, adjustable via CFG1[ADIV] to a division factor of 1, 2, 4, or 8. For specific ADC frequency requirements, refer to the device Data Sheet.

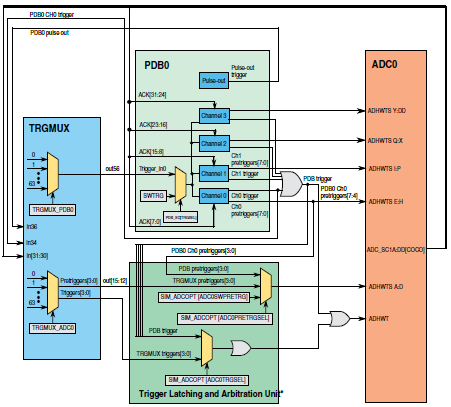

Trigger and their sources

-> In ADC systems, triggers are signals that start the conversion process for the complete ADC block(ADC0 or ADC1), while by pre-triggers we mean the ADC channels of the ADC instance, whose conversion has to be done before the conversion of the whole ADC instance begins. Now there are 2 types of ADC Triggers in S32K1xx MCU:

- ADC Software Trigger: By writing some bit value to ADC peripheral Register, after that ADC conversion is started.

- ADC Hardware Trigger: By configuring some external ADC hardware event and after that ADC conversion starts

ADC Software Triggering:

- By writing bit value to ADC Peripheral registers. SC1A and its last 6 bits. In last 6 bits we put value of which ADC channel we want to start the ADC conversion.

ADC Software Trigger ADC Hardware Triggering

-> ADC triggers and pre-triggers conversions we can start via hardware external events through use of, the Programmable Delay Block (PDB) or Trigger Multiplexer (TRGMUX).

PDB Triggering: PDB peripheral is provided specifically for trigger support in ADC. It triggers ADC conversions and controls channels via up to 8 pre-triggers( meaning 8 ADC channel pins), reducing CPU involvement. Each PDB pairs with an ADC (PDB0-ADC0, PDB1-ADC1).

TRGMUX Triggering: As we understood how PDB is an ADC-specific peripheral for triggering, similarly TRGMUX is a triggering peripheral for all peripherals available in MCU. TRGMUX also offers flexible ADC triggers using external/internal signals. Modules like CMP, LPIT, RTC, and LPTMR can trigger the ADC. TRGMUX enables different peripherals to start ADC conversions without the PDB.

-> The trigger source is controlled by SIM_ADCOPT[ADCxTRGSEL], allowing the selection of PDB or TRGMUX based on application needs.

- So its PDB is specially for ADC triggering and TRGMUX is for triggering of all peripheral.

- So we will use PDB to trigger ADC and PDB will be triggered through TRGMUX and TRGMUX will be connected to other peripheral for hardware inputs.

-> Hardware Triggering Schemes:

Default Scheme (PDB): The most common method is using the PDB to trigger the ADC. This approach is suggested for general use because of its simplicity and automatic trigger mechanism made dedicatedly for ADC.

Alternative Scheme (TRGMUX): TRGMUX provides another option for hardware triggering, offering more flexibility in selecting which peripherals or pins will initiate ADC conversions.

-> The SIM_ADCOPT[ADCxTRGSEL] field is used to control and configure the source of ADC triggers, allowing the system to choose between PDB or TRGMUX based on the application’s needs.

To completely understand this Block Diagram, follow our course on AUTOSAR ADC.

Trigger Selection for ADC

–> You can select any combination of trigger enable and trigger for the ADC, but once selected, they cannot be changed on-the-fly. There are specific steps for switching the trigger or pre-trigger sources:

–> To Change the Trigger Source:

- Stop the current trigger generation.

- Wait for 2.5 cycles of the ADC operating clock and 1.5 cycles of the ADC host interface clock, allowing the last trigger to latch.

- Check the

ADC_SC2[TRGSTLAT]status until it becomes 0, indicating all queued conversions are completed. - Update the trigger source as needed.

- Restart the trigger generation unit.

–> For Immediate Trigger Change:

- Stop the current trigger generation.

- Flush the queued triggers by setting

ADC_CFG1[CLRLTRG], except the one currently in progress. - Wait for 2.5 cycles of the ADC operating clock.

- Check

ADC_SC2[TRGSTLAT]until it becomes 0. - Update the trigger source.

- Restart the trigger generation unit.

–> Note: If these steps aren’t followed, some triggers might be missed without being reported.

ADC Trigger and Pre-Trigger Configuration

–> The ADC supports two main triggering schemes, as previously explained, through these two paths (using the ADC0_PDB0 triggering example):

- Direct Triggering Path: Used through the PDB starting from channel 4 onward.

- Multiplexed Triggering Path: Utilizes PDB/TRGMUX for channels 0 to 3 via a trigger latching mechanism.

–> When configuring the ADC, you can either:

- Use the direct triggering path with PDB for channels 4 and above, while using PDB for channels 0 to 3, or

- Use only the TRGMUX path for channels 0 to 3.

–> For the PDB direct triggering scheme, ensure that pre-triggers are spaced at least 4 bus clock cycles apart. The table below outlines the ADC triggering configurations and their behavior based on these paths.

–> Note: The PDB only signals a sequence error if two consecutive pre-triggers come from the same PDB channel. If different PDB channels are used, it is important for the software to ensure that there is at least a 4-bus clock cycle delay between the pre-triggers. Otherwise, both conversion results will be invalid.

> Selectable Hardware Conversion Trigger with Hardware Channel Select

- ADHWT is considered as a trigger for each ADC peripheral whereas ADHWTSn is a pretrigger for each channel of ADC peripheral.

Enabling Trigger:

- ADHWT is enabled when

SC2[ADTRG] = 1and a hardware pre-trigger event (ADHWTSn) occurs. - Not all MCUs support this; check your MCU’s ADC documentation for details.

- ADHWT is enabled when

Trigger Operation:

- A conversion starts on the rising edge of ADHWT after the hardware pre-trigger (

ADHWTSn) event. - If a conversion is already in progress, new triggers are ignored.

- A conversion starts on the rising edge of ADHWT after the hardware pre-trigger (

Continuous Conversion:

- In continuous mode, only the first rising edge triggers the ADC.

- The ADC keeps converting using the same

SCnconfiguration until aborted.

Trigger Conditions:

- Ensure

ADHWTSnis set before ADHWT is triggered. - If

ADHWTSnchanges during a conversion, it must remain asserted until the conversion finishes.

- Ensure

Channel and Results:

- Active trigger signals decide the channel and result register:

- ADHWTSA selects SC1A and stores results in RA.

- ADHWTSn selects SC1n and stores results in Rn.

- The respective conversion complete flag (SC1n[COCO]) is set after the conversion, and an interrupt is triggered if enabled (

SC1[AIEN]=1).

- Active trigger signals decide the channel and result register:

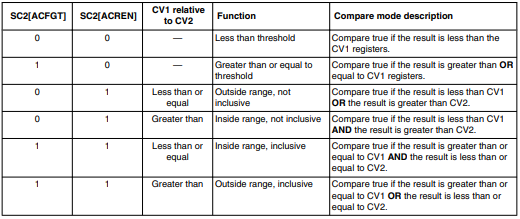

> Automatic Compare with Interrupt for less-than, greater-than, or equal-to, within range, or out-of-range

- As the heading might be self-explanatory, this function helps compare the conversion value with user-pre-defined values. These compare values are referred to as CV1 and CV2.

- The Compare Value Registers (CV1 and CV2) contain a compare value used to compare the conversion result when the compare function is enabled, that is, SC2[ACFE]=1.

- The compare mode is determined by SC2[ACFGT], and SC2[ACREN].

- After the input is sampled and converted, the compare values in CV1 and CV2 are used as described in the following table. There are Six Compare Modes as shown in the following table:

With

SC2[ACREN] = 1:If

CV1 <= CV2:- Setting

SC2[ACFGT]: Triggers if the value is inside the range (inclusive of endpoints). - Clearing

SC2[ACFGT]: Triggers if the value is outside the range (not inclusive of endpoints).

- Setting

If

CV1 > CV2:- Setting

SC2[ACFGT]: Triggers if the value is outside the range (inclusive of endpoints). - Clearing

SC2[ACFGT]: Triggers if the value is inside the range (not inclusive of endpoints).

- Setting

- If the condition selected evaluates true, SC1n[COCO] is set.

- When a conversion finishes and the compare function is enabled:

- If the compare condition is not met,

SC1n[COCO]remains unset, and the conversion result is not transferred to the result registerRn. - If hardware averaging is enabled, the compare function checks the averaged result against the compare values, which means that if both hardware averaging and compare function are enabled together then first hardware averaging is performed and then the comparing function. The same compare conditions apply as usual.

- An ADC interrupt is generated when

SC1n[COCO]is set, provided that the ADC interrupt is enabled (SC1n[AIEN] = 1).

- If the compare condition is not met,

- NOTE: The compare function can monitor the voltage on a channel while the MCU is in Wait or Normal Stop mode. The ADC interrupt wakes the MCU when the compare condition is met.

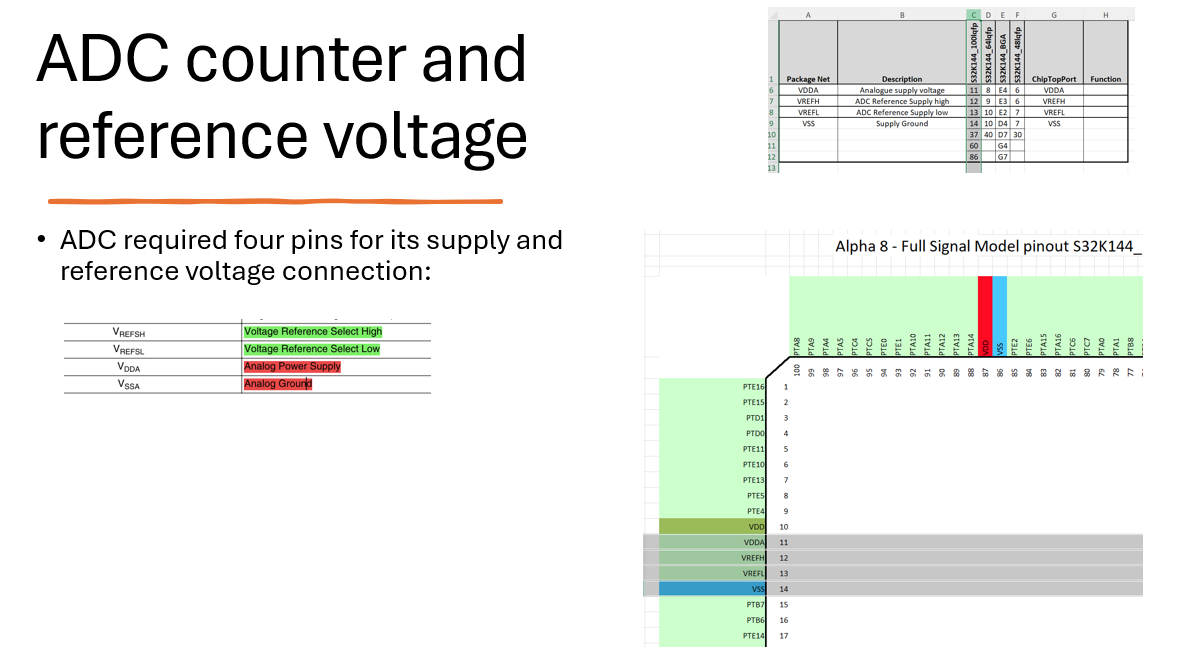

> Selectable Voltage Reference: External or Alternate

- The ADC can be set to use one of two voltage reference pairs for conversions:

- VREFSH and VREFSL – These provide the reference voltage.

- Each pair includes:

- A positive reference (VREFSH) should be between the minimum reference voltage high and VDDA.

- A ground reference (VREFSL) at the same potential as VSSA.

- Each pair includes:

- VREFSH and VREFSL – These provide the reference voltage.

- The ADC can be set to use one of two voltage reference pairs for conversions:

- Reference options:

- External reference pair: VREFH and VREFL.

- Alternate reference: VALTH, which can be an additional external pin or an internal source, based on the MCU configuration.

- Reference options:

- The reference source is selected using

SC2[REFSEL]. Refer to the specific MCU’s configuration details for more on voltage reference options.

ADC Reference Voltage selections

> Self-Calibration Mode

- Self-calibration in an ADC is a feature that helps improve its accuracy by automatically adjusting for internal errors, offsets, and gain variations.

- Internal errors can be multiple but we’ll discuss some common errors that as Noise(Unwanted fluctuations in the ADC’s output due to electrical interference) or Temperature Drift(Change in ADC characteristics due to temperature fluctuations).

- Offsets and Gain are directly linked to ADC conversion which can make the most prominent error in ADC conversion. But gain error and offset error are a wide concept, therefore rather than understanding the gain error and offset error we’ll focus on the effect of Gain and Offset on the ADC conversion.

- Gain defines the slope of the relationship between the analog input voltage and the digital output value.

Consider a 10-bit ADC with a 5V reference:

- Correct Gain: 5V corresponds to 1023 (maximum digital value), with each step representing approximately 0.00488V.

- Under-scaled Gain: 5V might correspond to only 512, meaning each step represents a larger increment, e.g., 5V/512 steps ≈ 0.00977V. This reduces the resolution and could miss small variations.

- Over-scaled Gain: 5V might correspond to 1023 even with a much lower input, e.g., 2.5V, meaning the ADC can’t distinguish input voltages above a certain threshold.

- Offset in an ADC is the deviation in the output when the input is zero. In an ideal ADC, if you provide a zero-voltage input, the digital output should be zero as well.

Consider a 10-bit ADC with a 5V reference:- Correct Offset: A zero input produces a digital output of 0, and a full-scale input of 5V corresponds to 1023.

- Positive Offset: A zero input produces a digital output of, say, 10. This means all readings will be shifted by +10. For instance, an input of 1000mV would output 522 instead of 512.

- Negative Offset: A zero input produces a digital output of -5. Now, an input of 1000mV would output 507 instead of 512.

- Gain defines the slope of the relationship between the analog input voltage and the digital output value.

- As we witnessed above how small error can make greater changes in final conversion. Therefore, calibration is important for ADC to give the highest accuracy(specified in the datasheet).

- NOTE: It is mandatory to calibrate the ADC after power-up or reset. Not doing this can result in ADC conversion results with lower than specified accuracy.

To calibrate the ADC correctly, follow these simplified steps:

- Wait for Stabilization: Ensure the reference voltage (VREFH) is stable before starting.

- Recalibrate After Reset: Calibrate the ADC after every system reset.

- One ADC at a Time: Calibrate only one ADC instance (e.g., ADC0) at a time. Make other instances idle.

- Set ADC Clock: Set the ADC clock (ADCK) to a value no higher than half the maximum frequency.

- Clear Calibration Registers: Clear calibration registers (CLPS, CLP3-CLP0, CLPX, CLP9) by writing 0000_0000h to them.

- Start Calibration: Write

SC3[CAL] = 1,SC3[AVGE] = 1, andSC3[AVGS] = 11bto start calibration. - Wait for Completion: Wait until the calibration is done (indicated by

SC1n[COCO] = 1). - Reconfigure: After calibration, you can adjust the ADC settings like clock speed and hardware averaging for your application.

- Now you very a great backend understanding of calibration working in ADC Self-Calibration.

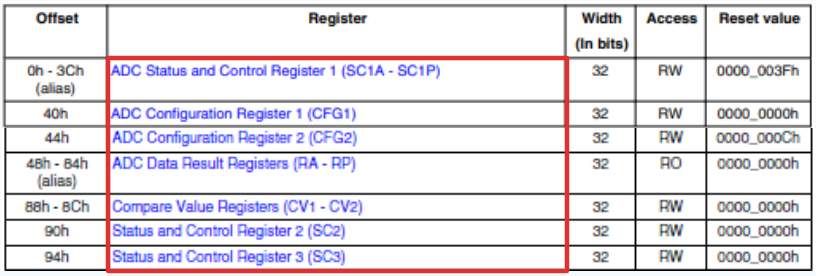

ADC-PERIPHERAL REGISTER

- In this section, we’ll match the above learning features of the ADC Peripheral with Microcontroller Registers.

- Above mentioned image demonstrates all the active registers in the ADC peripheral. But our main focus of interest is SC1n, SC2, SC3, CFG1, CFG2, Rn, CV1 and CV2 registers. . This contains our learned feature of the ADC Peripheral.

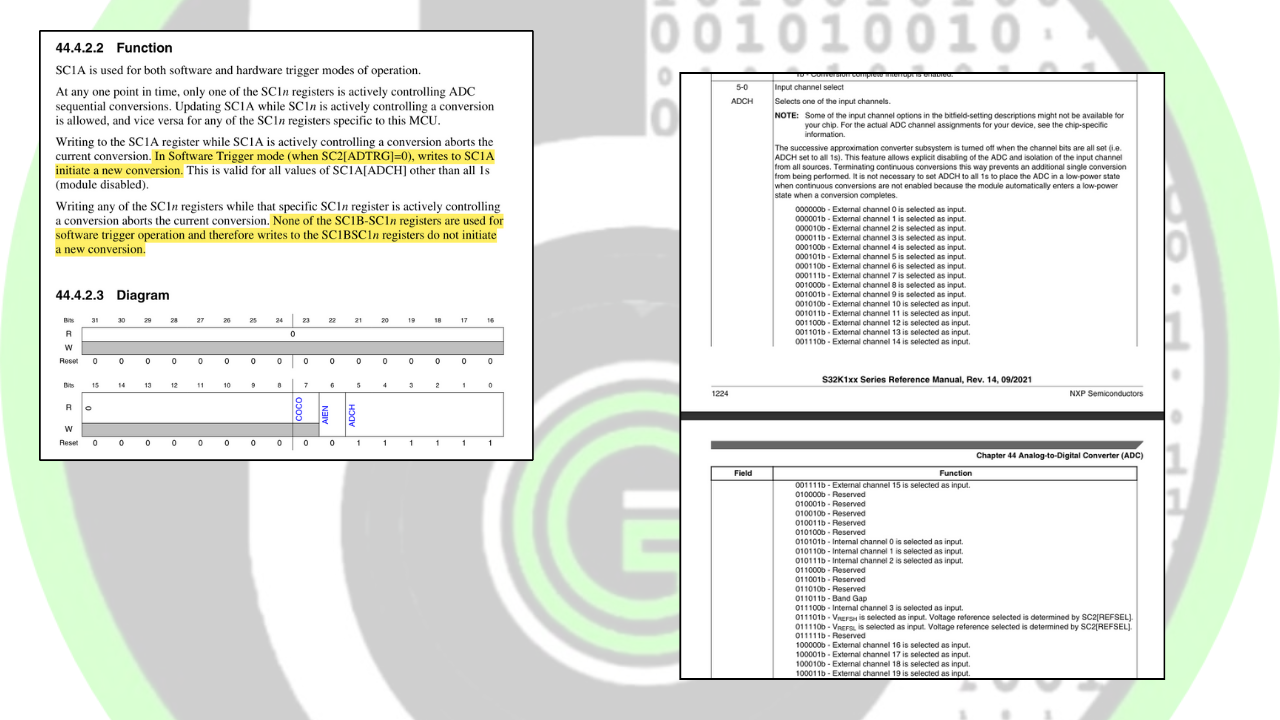

> SC1n(ADC Status and Control Register 1)

- Function of the Register

- SC1A Register: It can control both software and hardware triggers for ADC conversions.

- You can update SC1A even if another SC1n register is actively controlling a conversion.

- Updating SC1A during an active conversion will abort the current conversion.

- In Software Trigger Mode (when

SC2[ADTRG] = 0), writing to SC1A starts a new conversion (as long asSC1A[ADCH]is not set to “all 1s”).

SC1B to SC1n Registers: These registers are not used for software-triggered conversions.

Writing to these registers does not start a new conversion.

- SC1A Register: It can control both software and hardware triggers for ADC conversions.

- Field of the Register

- COCO: The COCO (Conversion Complete) flag is set each time a conversion finishes, based on specific conditions:

- COCO is set when:

The compare function is off (SC2[ACFE] = 0) and the hardware average function is disabled (SC3[AVGE] = 0).

The compare function is on (SC2[ACFE] = 1), and the compare result is true.

The hardware average function is enabled (SC3[AVGE] = 1), and the set number of conversions (determined by AVGS) is completed.

A calibration sequence completes.

COCO is cleared when:

The respective SC1n register is written.

The respective result (Rn) register is read.

COCO Flag Values:

0b: Conversion not completed.

1b: Conversion completed.

- AIEN: Interrupt Enable (AIEN) controls whether a conversion complete interrupt is triggered: When COCO is set and AIEN is 1 (enabled), an interrupt occurs.

AIEN Flag Values:

0b: Interrupt disabled.

1b: Interrupt enabled.

- ADCH: Input Channel Select (ADCH) defines the input channel for the ADC. Setting all ADCH bits to 1 disables the ADC, isolating the input channel and ending continuous conversions to prevent extra conversions. If continuous conversions are not enabled, the ADC automatically enters low-power mode after a conversion completes.

- Channel Bitfield Assignments:

000000b– External channel 0 selected.000001b– External channel 1 selected.- …

001111b– External channel 15 selected.010000bto010100b– Reserved.010101b– Internal channel 0 selected.010110b– Internal channel 1 selected.010111b– Internal channel 2 selected.011000bto011010b– Reserved.011011b– Band Gap selected.011100b– Internal channel 3 selected.011101b– VREFSH selected (voltage reference determined bySC2[REFSEL]).011110b– VREFSL selected (voltage reference determined bySC2[REFSEL]).011111b– Reserved.100000b– External channel 16 selected.- …

101111b– External channel 31 selected.110000bto111110b– Reserved.111111b– Module disable.

- Channel Bitfield Assignments:

- Function of the Register

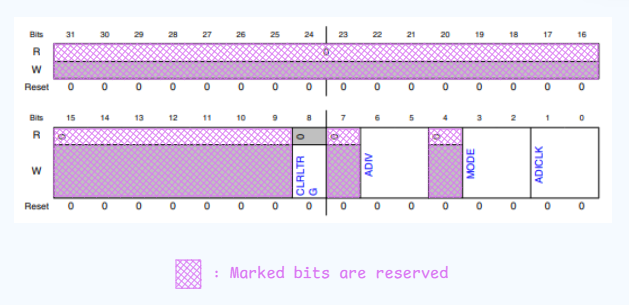

> ADC Configuration Register 1 (CFG1)

-

- Function of the Register

- Configuration Register 1 (CFG1) selects the mode of operation, clock source, and clock divide.

- Field of the Register

-

CLRTRG: The “Clear Latch Trigger” (CLRLTRG) field in the trigger handler block is a control mechanism to reset all latched triggers except the one actively being processed. Here’s a breakdown of how it functions:

- Trigger Clear Action: Writing

1to this bit will clear all latched triggers, allowing the system to reset any queued triggers, thus avoiding unnecessary re-triggering. However, the current processing trigger remains unaffected. - No Effect on Writing

0: Setting this bit to0doesn’t alter the state of the latches, which means they stay as they are. - Self-Clearing Bit: The CLRLTRG bit self-clears immediately after being set to

1. This self-clearing behavior ensures minimal intervention after issuing a clear command.

Important Notes

- Waiting Period: After setting CLRLTRG to

1, wait for at least 2.5 ADC clock cycles to ensure all latches have fully cleared before proceeding. - Instance Limitations: The CLRLTRG field isn’t universally supported. For instance:

- It is not supported in

ADC0_CFG1. - It is supported in

ADC1_CFG1.

- It is not supported in

- Trigger Clear Action: Writing

-

ADIV(Clock Divide Select): The field sets how much to divide the input clock to generate the ADC’s internal clock (ADCK). Here’s a simplified breakdown:

00– No division (ADCK = input clock)01– Divide by 2 (ADCK = input clock / 2)10– Divide by 4 (ADCK = input clock / 4)11– Divide by 8 (ADCK = input clock / 8)

-

MODE(Conversion mode selection): The field sets the ADC’s resolution for conversions:

00– 8-bit resolution01– 12-bit resolution10– 10-bit resolution11– Reserved

-

ADICLK: The field chooses the input clock source for the ADC’s internal clock (ADCK). Here are the options:

00– Use Alternate Clock 1 (ALTCLK1)01– Use Alternate Clock 2 (ALTCLK2)10– Use Alternate Clock 3 (ALTCLK3)11– Use Alternate Clock 4 (ALTCLK4)

Refer to your device’s clocking chapter for specific details on each alternate clock.

-

- Function of the Register

> ADC Configuration Register 2 (CFG2)

- Function of the Register

- Configuration Register 2 (CFG2) selects the long sample time duration during a long sample mode.

- Field of the Register

The SMPLTS field sets the ADC’s sample time, allowing adjustments based on input impedance or desired conversion speed. Here’s how it works:

- Sample Time Range: You can select a sample time between 2 and 256 ADCK clock cycles.

- Setting Value: The value entered here should be the desired sample time minus 1 (e.g., for a sample time of 4 cycles, set

SMPLTS = 3).. - Power Efficiency: Longer sample times can reduce power usage during continuous conversions if high conversion rates aren’t essential.

- Function of the Register

> ADC Data Result Registers (RA – aRP)

Function of the Register

The Data Result Registers (Rn) store the results of ADC conversions, with each register linked to a specific channel set by the corresponding Status and Channel Control Register (SC1). Key points about these registers include:

- One-to-One Mapping: Each SC1 register has a unique corresponding Rn register to store the conversion result for its selected channel.

- Unused Bits: Any unused bits in the Rn register are cleared to

0. - Read-Only: The Rn registers are read-only. Attempting to write to them will generate a transfer error.

The table you add will provide further detail on register behavior across various ADC operation modes.

- Field of the Register

- D: Data Result

- Field of the Register

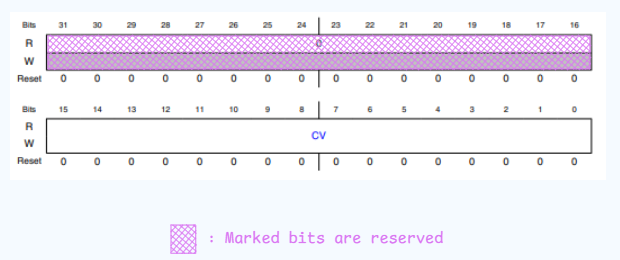

> Compare Value Registers (CV1 – CV2)

- Function of the Register

The Compare Value Registers (CV1 and CV2) hold values used to compare against ADC conversion results when comparison is enabled (SC2[ACFE] = 1).

- Same Format as Rn: CV1 and CV2 have the same format as the data result (Rn) registers.

- Using CV2: CV2 is only used if the compare range function is enabled (SC2[ACREN] = 1).

- Field of the Register

- CV: Compare Value

- Function of the Register

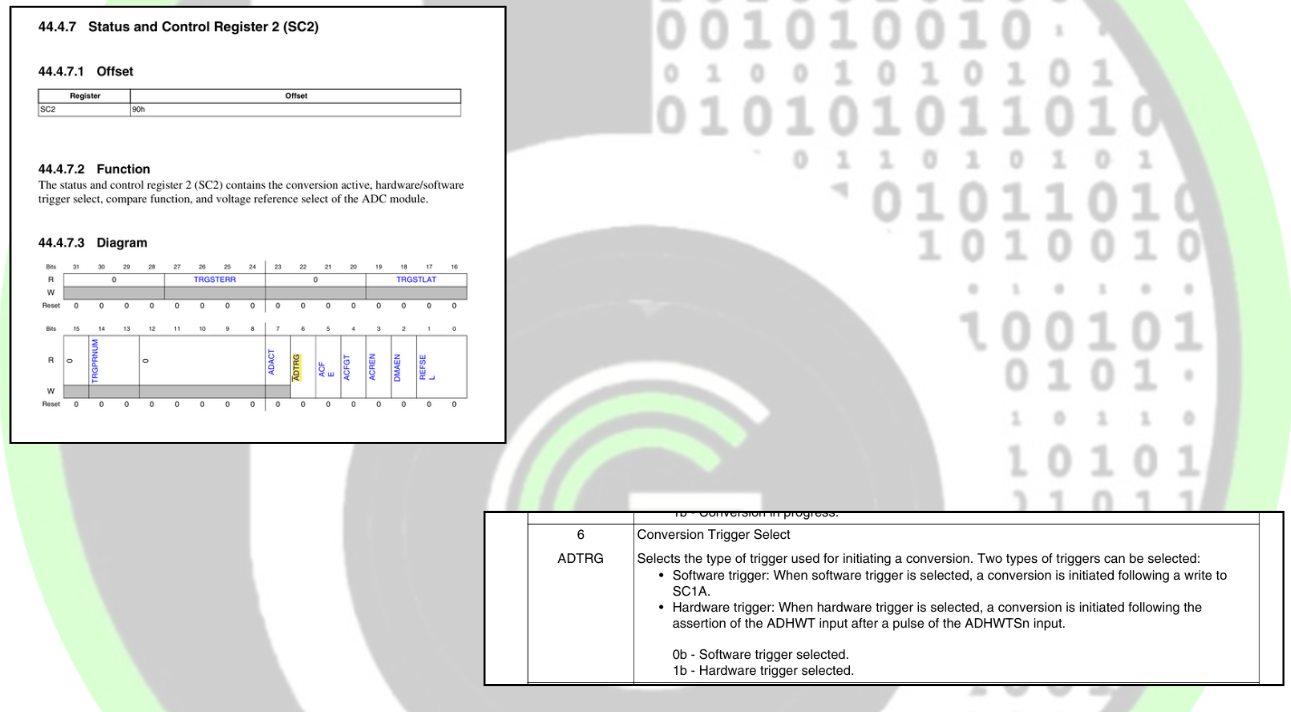

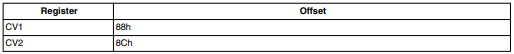

> Status and Control Register 2 (SC2)

- Function of the Register

- The status and control register 2 (SC2) contains the conversion active, hardware/software trigger select, compare function, and voltage reference select of the ADC module.

- Field of the Register

TRGSTERR: The field signals errors in multiplexed trigger requests for ADC conversions, indicating if a trigger was missed because it was either already latched or being processed. Here’s how it works:

Clearing Errors: Write

1to a bit in this field to clear an error for that specific trigger.Bit Mapping: Each bit corresponds to an individual trigger:

- Bit 24 – Trigger request 0

- Bit 25 – Trigger request 1

- Bit 26 – Trigger request 2

- Bit 27 – Trigger request 3

Error Status:

0000– No errors0001– Error has occurred

Support Note: This field is only supported in

ADC1_SC2, notADC0_SC2.TRGSTLAT: The field indicates the status of multiplexed hardware trigger requests, showing whether a trigger has been latched for processing. Here’s how it works:

Bit Mapping: Each bit corresponds to an individual trigger:

- Bit 16 – Trigger request 0

- Bit 17 – Trigger request 1

- Bit 18 – Trigger request 2

- Bit 19 – Trigger request 3

Latch Status:

0000– No trigger request has been latched0001– A trigger request has been latched

Support Note: This field is only supported in

ADC1_SC2, notADC0_SC2.TRGPRNUM: The field indicates the trigger number that is currently being serviced, but it must be interpreted alongside the corresponding TRGSTLAT status bits. Here’s how it works:

Valid TRGPRNUM Values: Each trigger number is valid only if the corresponding TRGSTLAT bit is set to

1:TRGPRNUM = 00is valid if TRGSTLAT[16] = 1 (trigger request 0 is latched).TRGPRNUM = 01is valid if TRGSTLAT[17] = 1 (trigger request 1 is latched).TRGPRNUM = 10is valid if TRGSTLAT[18] = 1 (trigger request 2 is latched).TRGPRNUM = 11is valid if TRGSTLAT[19] = 1 (trigger request 3 is latched).

Potential Mismatch: Sometimes there may be a mismatch between the TRGPRNUM value and the ideal trigger selected by the TRGSTLAT bits due to synchronization delays between the TRGSTLAT field and the hardware logic. The TRGSTLAT field updates first, but the hardware operates on a delayed version of it, so any triggers arriving during this synchronization period may not immediately be presented to the hardware.

Support Note: This field is only supported in

ADC1_SC2, notADC0_SC2.ADACT: The field indicates whether an ADC conversion or hardware averaging is currently in progress:

0– Conversion not in progress1– Conversion in progress

It is set when a conversion starts and cleared once the conversion is completed or aborted.

ADTRG: The field selects the trigger type for starting an ADC conversion:

0– Software trigger: A conversion starts when software writes to the SC1A register.1– Hardware trigger: A conversion starts when the ADHWT input is asserted after a pulse from the ADHWTSn input.

ACFE: The field enables or disables the compare function for the ADC:

0– Compare function disabled1– Compare function enabled

ACFGT: The field configures the compare function to check if the ADC conversion result is greater than the values in CV1 and CV2, depending on the ACREN setting.

- Effect: ACFGT only has an effect when the ACFE field is enabled (set to

1). - Purpose: It allows the compare function to trigger based on whether the conversion result exceeds the compare values.

- Effect: ACFGT only has an effect when the ACFE field is enabled (set to

ACREN: The field enables the compare function to check if the ADC conversion result falls within (or outside) the range defined by CV1 and CV2, based on the setting of ACFGT.

- Effect: ACREN works in conjunction with ACFE (enabled) and ACFGT to determine if the conversion result is within or outside the range of CV1 and CV2.

- Compare Modes: If ACREN is enabled, the result is compared against the range determined by CV1 and CV2, depending on the ACFGT setting.

DMAEN: The field controls whether DMA (Direct Memory Access) is enabled for ADC conversion events:

0– DMA disabled: DMA will not be used.1– DMA enabled: DMA will assert the ADC DMA request when a conversion is complete, indicated by the COCO flag being set in the SC1n register.

REFSEL: The field selects the voltage reference source used for ADC conversions:

00– Default voltage reference: Uses the external reference voltage pins VREFH and VREFL.01– Alternate reference voltage: Uses VALTH as the reference, which may be an additional external pin or an internal source, depending on the MCU configuration. Refer to the chip configuration details for specifics.10– Reserved11– Reserved

- Function of the Register

> Status and Control Register 3 (SC3)

- Function of the Register

- The Status and Control Register 3 (SC3) controls the calibration, continuous conversion, and hardware averaging functions of the ADC module.

- Field of the Register

CAL: The field controls the ADC calibration process:

- When CAL = 1: The ADC starts the calibration sequence. This bit remains set during the calibration and is cleared once the calibration is complete.

- During Calibration:

- The calibration cannot be interrupted by register writes, as this would invalidate the results.

- Any ongoing conversion is aborted when calibration is started.

- It is mandatory to use averaging with an average count of 32 for accurate calibration.

- If multiple ADCs are present on the device, they must be calibrated one at a time, as parallel calibration can cause interference between the ADCs..

ADCO: The field enables or disables continuous ADC conversions:

0– One conversion: A single conversion (or a set of conversions if AVGE is enabled) will be performed after the conversion is initiated.1– Continuous conversions: The ADC will continuously perform conversions (or continuously perform sets of conversions if AVGE is enabled) after the initial conversion is started.

AVGE: The field enables or disables the hardware averaging function of the ADC:

0– Hardware average disabled1– Hardware average enable.

AVGS: The field selects the number of ADC conversions to be averaged for the final result:

00– 4 samples averaged01– 8 samples averaged10– 16 samples averaged11– 32 samples averaged

- Function of the Register