Introduction

Today in this series, we’ll learn how SPI communication takes place in the microcontroller. For those who want to learn about SPI communication on bit-level data transmission, they can redirect to this BLOG. SPI is a common peripheral in almost every MCU, and its versatility makes it a go-to choice for many applications.

Understanding SPI Communication in a Single Session

In the above-mentioned example session of SPI communication, the first thing we can see is an idle clock state before the Data Transmission began from the Master Side via MOSI. This means CPOL(Clock Polarity) = 0. We can also observe first bit is sampled at the first of the Clock, meaning the CPHA(Clock Phase) = 0 through which we can conclude the that taken example is running SPI communication in MODE 0. One more important thing to observe is that will complete data is communicated the CS pin is low, which denotes that this helps us detect a complete session of SPI communication as well as helps in choosing different slaves by pulling different CS of different slaves. We can also additionally observe how the first master transmitted 1 byte of data “0x9F” in response to which the slave responded with 3-byte of data “0xEE, 0x00 and 0x30”.

SPI Pin Configuration

SPI (Serial Peripheral Interface) is a flexible protocol with variations in its wiring setup. Let’s get into the 3-wire and 4-wire configurations to understand how they work and differ.

4-Wire SPI Configuration (Standard SPI)

Pins Used:

- MOSI (Master Out, Slave In): Transmits data from the master to the slave.

- MISO (Master In, Slave Out): Sends data from the slave to the master.

- SCK (Serial Clock): Synchronizes communication between master and slave.

- CS/SS (Chip Select/Slave Select): Activates the desired slave device.

How It Works:

- The master generates the clock (SCK) and sends/receives data on MOSI and MISO, respectively.

- The CS/SS pin ensures only one slave communicates at a time in a multi-slave setup.

- Communication is full-duplex (data sent and received simultaneously).

–> Use Case: 4-wire SPI is widely used for devices requiring fast and reliable data transfer, such as memory chips, sensors, and displays.

3-Wire SPI Configuration

Pins Used:

- SCK (Serial Clock): Synchronizes communication.

- SDA (Single Data Line): Combines data transmission and reception on one shared line.

- CS/SS (Chip Select/Slave Select): Selects the slave for communication.

How It Works:

- The SDA line acts as a bidirectional data line, toggling between input (MISO) and output (MOSI) modes.

- The master controls when the line switches from transmitting to receiving.

- Communication is half-duplex (data sent and received alternately, not simultaneously).

–> Use Case: 3-wire SPI is used in applications where fewer GPIO pins are available, such as compact or low-power devices.

Comparison: 3-Wire vs. 4-Wire SPI

| Aspect | 4-Wire SPI | 3-Wire SPI |

|---|---|---|

| Data Lines | Separate lines: MOSI & MISO | Single shared line: SDA |

| Communication Type | Full-duplex | Half-duplex |

| Speed | Faster (simultaneous data) | Slower (alternating data) |

| Complexity | Requires more pins | Reduces pin usage |

| Applications | High-speed communication | Low-pin, resource-constrained setups |

SPI Communication: Interrupt, Polling, and DMA

–> SPI communication can be implemented using different methods to handle data transmission and reception: Polling, Interrupts, and DMA (Direct Memory Access). Let’s break these down quickly and simply.

1. Polling

–> In polling, the CPU constantly checks the SPI status register to see if the transmission or reception is complete.

How It Works:

- The master initiates SPI communication and waits (polls) until the SPI status register indicates the operation is done.

- Once ready, it reads or writes the data.

Pros:

- Simple to implement.

- No external dependencies or complex setups.

Cons:

- CPU is stuck in a loop, wasting cycles.

- Inefficient for high-speed or large data transfers.

–> Example Use Case: Small, simple applications where data transfer is occasional or time-critical (e.g., reading sensor data once per second).

2. Interrupt

–> In interrupt-driven SPI, the CPU can perform other tasks while waiting for SPI events. When the transfer is complete, an interrupt is triggered to notify the CPU.

How It Works:

- SPI communication is initiated.

- The SPI peripheral triggers an interrupt upon completion.

- The CPU handles the interrupt and processes the data.

Pros:

- Efficient use of CPU time.

- Ideal for multitasking systems.

Cons:

- Requires interrupt setup and handling.

- Overhead due to frequent context switching in high-speed transfers.

–> Example Use Case: Applications needing multitasking, like managing multiple sensors or peripherals concurrently.

3. DMA

–> With DMA, the CPU is almost entirely freed from handling data transfer. The DMA controller moves data directly between memory and the SPI peripheral without CPU intervention.

How It Works:

- The CPU configures the DMA controller and starts the transfer.

- DMA handles the data transfer autonomously.

- The CPU receives a notification (via interrupt) when the transfer is complete.

Pros:

- Highly efficient, especially for large data transfers.

- CPU remains free for other tasks.

Cons:

- Requires a more complex setup.

- Only available in systems with DMA support.

–> Example Use Case: High-speed communication, such as transferring data to/from an SD card or LCD.

Quick Comparison Table

| Method | CPU Involvement | Speed | Best For |

|---|---|---|---|

| Polling | High (CPU busy waiting) | Slow (wastes time) | Simple, low-priority tasks |

| Interrupt | Moderate (on events only) | Medium (efficient) | Multitasking with small data |

| DMA | Low (almost no involvement) | Fast (direct access) | Large, high-speed data transfers |

SPI Chip Select (CS) Pin Configuration

–> The Chip Select (CS) pin in SPI communication determines which slave device is chosen to have communication. Different microcontrollers offer varying ways to handle the CS pin: some integrate it directly within the SPI module, while others allow it to be configured separately. Let’s explore both approaches.

CS Pin Managed by the SPI Module

–> With module-managed CS, the SPI peripheral hardware takes full control of the CS pin, automatically toggling it during data transfers. This simplifies implementation, reduces timing errors, and ensures precise synchronization with the SPI clock and data signals. However, it often limits flexibility, as you must use the designated CS pin associated with the SPI module, and multi-slave configurations can be challenging.

Separately Configured CS Pin

–> Manually configured CS pins offer greater flexibility by allowing any GPIO pin to serve as the CS. In this approach, the firmware controls the CS pin manually by driving it low to activate or high to deactivate, enabling custom multi-slave setups. While this approach supports more complex configurations, it requires additional coding effort and careful handling of timing to avoid errors.

–> Conclusion: The choice between the two depends on the application: module-managed CS is ideal for simpler systems with fewer slaves, whereas manually configured CS is better suited for complex setups requiring multiple slaves or custom configurations.

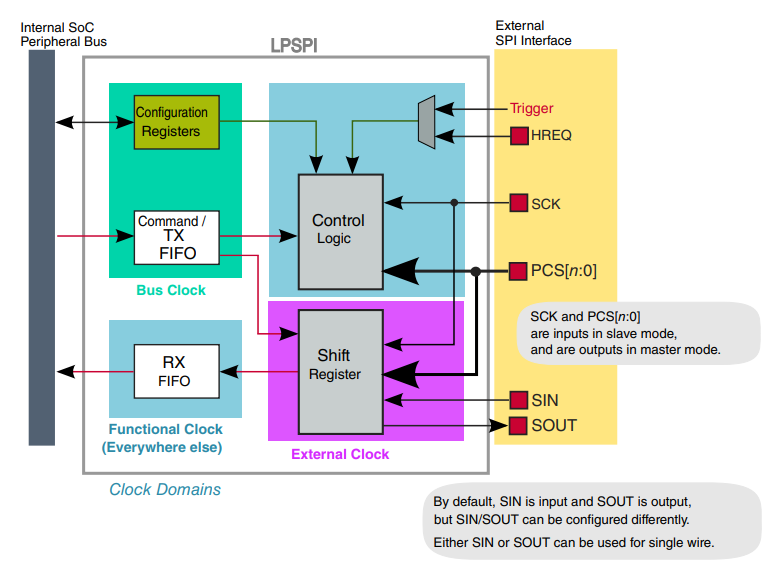

SPI Block Diagram (with Registers)

–> This SPI block diagram highlights the core functional units that make data transmission and reception efficient in SPI communication. Here’s a concise explanation of the main components:

1. Configuration Registers:

- These registers store settings for SPI operation, such as SPI mode (CPOL, CPHA), data frame size, and clock configurations.

- Role: Acts as the starting point for initializing and customizing the SPI module to meet specific communication needs.

2. TX FIFO (Transmit FIFO):

- A temporary buffer that holds data to be transmitted. Data written to this FIFO is queued and sent to the shift register for serial transmission.

- Role: Ensures smooth and uninterrupted outgoing data flow during SPI communication.

3. RX FIFO (Receive FIFO):

- A buffer that collects incoming serial data after being converted into parallel format by the shift register. The processor reads data from this buffer.

- Role: Prevents loss of received data by queuing it for processing.

4. Shift Register:

- The core component that handles the conversion between serial and parallel data.

- It shifts out data from TX FIFO bit-by-bit on the SOUT line and simultaneously shifts in data bit-by-bit on the SIN line.

- Role: Manages real-time serial-to-parallel and parallel-to-serial data conversion.

5. Control Logic:

- The central unit that orchestrates data flow, timing, and SPI operations. It handles sequencing, manages interrupts, and ensures proper communication protocols are followed.

- Role: Provide the intelligence to coordinate the smooth operation of SPI communication.

Summary

–> These components work together to ensure that SPI communication is efficient and reliable. The configuration registers set up the module, the FIFOs manage data flow, the shift register performs bit-level operations, and the control logic oversees everything. Each plays a distinct but interconnected role.