About GPIO Peripheral

GPIO is a peripheral in Microcontroller for using the MCU pins as transmitting and receiving of raw digital signals.

In the case of transmitting, it is said as Output pin and in the case of receiving it is said as Input pin. And by raw digital signals, we mean Digital High or Digital Low signal.

Input direction of GPIO pin

In the case of Input direction, MCU pin can detect which type of external signal data is fed into it. That is whether High Digital signal (+5) or Low Digital signal (GND).

Like in the case of Switch, connected to MCU pin, as we press the switch, we send high signal and when we unpressed the switch we send low signal. So, this functionality is done via GPIO peripheral and by configuring it in input direction.

Also in Microcontroller, we can generate interrupt, as these digital High or Low signal is fed into them. These interrupts are called as Port Pin interrupts. The role of Input direction of MCU pin is also tilised in other communication peripherals as well where data is received by MCU.

Output direction of GPIO pin

In the case of Output direction, we can generate digital High (+5 or +3.3v) or digital Low(GND) signal from the Microcontroller pin.

Like in the case of LEDs, relays when we want to control some electric device by simple digital High and digital Low signals. Then output direction is used.

In the case of output direction, we can either generate Digital High signal or Digital Low signal

With Output direction there are some MCU to MCU features like pull up/pull down configuration and Drive strength

GPIO Introduction

Features of GPIO

–> Besides allowing the Pin DIrection to the microcontroller pin, the GPIO peripheral also keeps check of different parameters like Setting/Clearing/Toggling logic of Output Configured microcontroller pins, Logic capturing of Input Configured microcontroller pins, and Pin Disabling. You’ll also notice one more important thing GPIO peripheral registers are named with initials PORT. Let us understand all these features with the register-level of the microcontroller.

–> Note: The GPIO module operates with the system clock.

GPIO Register Description

- Port Data Output Register (PDOR)

- Port Set Output Register (PSOR)

- Port Clear Output Register (PCOR)

- Port Toggle Output Register (PTOR)

- Port Data Input Register (PDIR)

- Port Data Direction Register (PDDR)

- Port Input Disable Register (PIDR)

–> NOTE: Each of the above-mentioned registers is 32-bit width. As mentioned below, if you change the 18th bit(for example) for any reason, then your action will only be reflected on the 18th pin. Also, each port has its own above-mentioned set of registers.

Port Data Output Register (PDOR)

–> Function: This register sets the logic levels for each general-purpose output pin.

–> NOTE: Avoid modifying pin configuration registers for pins not in your package. This means that if your microcontroller has 18 pins of PORT A then you should not change 17th onwards bits of the register.

- Port Data Output:

- 0b – Logic level 0 is driven on the pin if it’s set for general-purpose output.

- 1b – Logic level 1 is driven on the pin if it’s set for general-purpose output.

- Port Data Output:

Port Set Output Register (PSOR)

–> Function: This register determines whether to set the fields of the PDOR.

- Port Set Output:

Writing to this register affects the corresponding bit in the PDOR:- 0b – No change to PDORn.

- 1b – Sets PDORn to logic 1.

- Port Set Output:

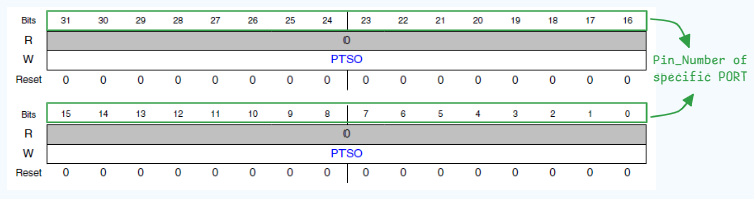

Port Clear Output Register (PCOR)

–> Function: This register clears the fields of the PDOR.

- Port Clear Output:

Writing to this register affects the corresponding bit in PDOR:- 0b – No change to PDORn.

- 1b – Clears PDORn to logic 0.

- Port Clear Output:

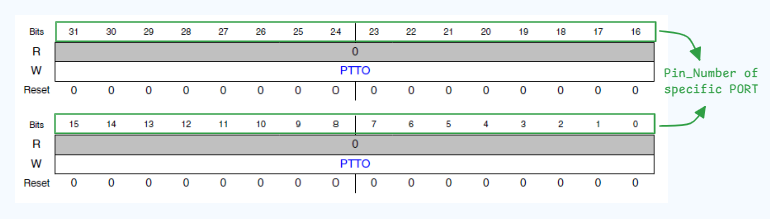

Port Toggle Output Register (PTOR)

–> Function: This register toggles the logic levels on each general-purpose output pin.

- Port Toggle Output:

Writing to this register affects the corresponding bit in the PDOR:- 0b – No change to PDORn.

- 1b – Sets PDORn to the opposite of its current state.

- Port Toggle Output:

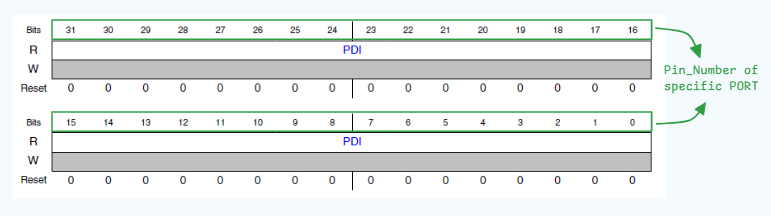

Port Input Disable Register (PIDR)

–> Function: This register captures the logic levels for each general-purpose input pin.

–> NOTE: Avoid modifying pin configuration registers for pins not in your package. Unbonded pins default to DISABLE for lower power consumption.

- Port Data Input:

- Reads 0 at unimplemented pins. Pins not set for digital functions read 0. If the Port Control and Interrupt module is off, the corresponding bit in PDIR won’t update.

- 0b – Logic level is 0 or not set for digital use.

- 1b – Logic level is 1.

- Port Data Input:

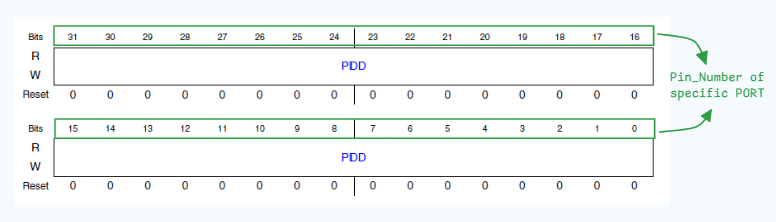

Port Data Direction Register (PDDR)

–> Function: The PDDR configures pins for input or output.

- Port Data Direction:

- 0b – Configures the pin as a general-purpose input (high-Z if the port input is disabled).

- 1b – Configures the pin as a general-purpose output.

- Port Data Direction:

Port Input Disable Register (PIDR)

–> Function: This register disables general-purpose pins from acting as inputs.

- Port Input Disable:

- 0b – Pin is set for General Purpose Input if configured for any digital function.

- 1b – Pin is not set as General Purpose Input; corresponding PDIR bit will read zero.

- Port Input Disable:

Conclusion

We are glad to see you here. If you are reading then you must have completed the learning of GPIO peripherals in S32K144. You can now have very brief control over GPIO peripherals where you know every functionality offered by S32K144 on their microcontroller as well as you know the bit-level understanding about how and which registers are meant to be monitored in a debugging process.

Feel free to connect us over our community support for any queries and give your important suggestions over this blog.