Add Your Heading Text Here

- FlexTIMER Module

- Low Power Interrupt Timer Module

- Low Power Timer

- Real Time Clock

About FTM (FlexTimer Module) Peripheral

FlexTimer Module is a 2-8 channel timer that supports input capture, output capture and generation of PWM signals to control electric motor and power managment applications.

- FTM time reference is a 16-bit counter that can be used as an unsigned or signed counter.

- FTM clock source is selectable:

- FTM Input Clock:

- Fixed Frequency clock:

- External clock:

- 16-bit counter:

- It can be a free running counter or a counter with initial/final value

- counting can be up or updown

Channel properties:

- Each channel can be configured for input capture, output capture or edge alligned PWM mode.

(In timer peripheral input capture is a feature in which some external pwm signal is )

- In Output compare mode, the output signal can be set, cleared or toggled on match

( in output compare mode, if the compore matches, we can either make the output signal to get High voltage, Low volatge or toggle)

- All channels can be configured for center-aligned PWM mode.

- Each pair of channels can be combined to generate a PWM signal with independent

control of both edges of PWM signal. - The FTM channels can operate as pairs with equal outputs, pairs with complementary outputs, or independent channels with independent outputs.

(explain 2 above combined)

- The deadtime insertion is available for each complementary pair.

(explain what is deadtime)

- Generation of match triggers

(trigger concept in timer peripheral)

- Dual edge capture for pulse and period width measurement.

Functional Blocks in FTM

FTM Clock Source

For running the timer peripheral, we would be needing some clock frequency.

So, we have to input the clock source to FTM peripheral.

The CLKS[1:0] bits select one of three possible clock sources for the FTM counter or

disable the FTM counter.

Prescaler

The selected counter clock source passes through a prescaler that is a 7-bit counter. The

value of the prescaler is selected by the PS[2:0] bits.

FTM Counter

FTM has a 16-bit counter that is used by the channels either for input or output modes.

- Up Counting:

Counter counts from x value to y value. X value is starting value of counter and then it increments till y value. CNTIN register defines start value( that is X ) and MOD register defines the final value that is Y.

In Up counting Y>X. QUADEN=0 and CPWMS=0.

FTM period when using up counting is (MOD-CNTIN + 0x0001) x period of counter clock.

Say MOD is 9999 abd CNTIN is 0 and period of counter clock is 10 ms.

So (((9999-0) +1)*.01) = 10 secs.

- Up-down counting:

Co

- Quadrature Decoder Mode:

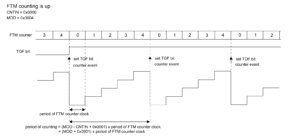

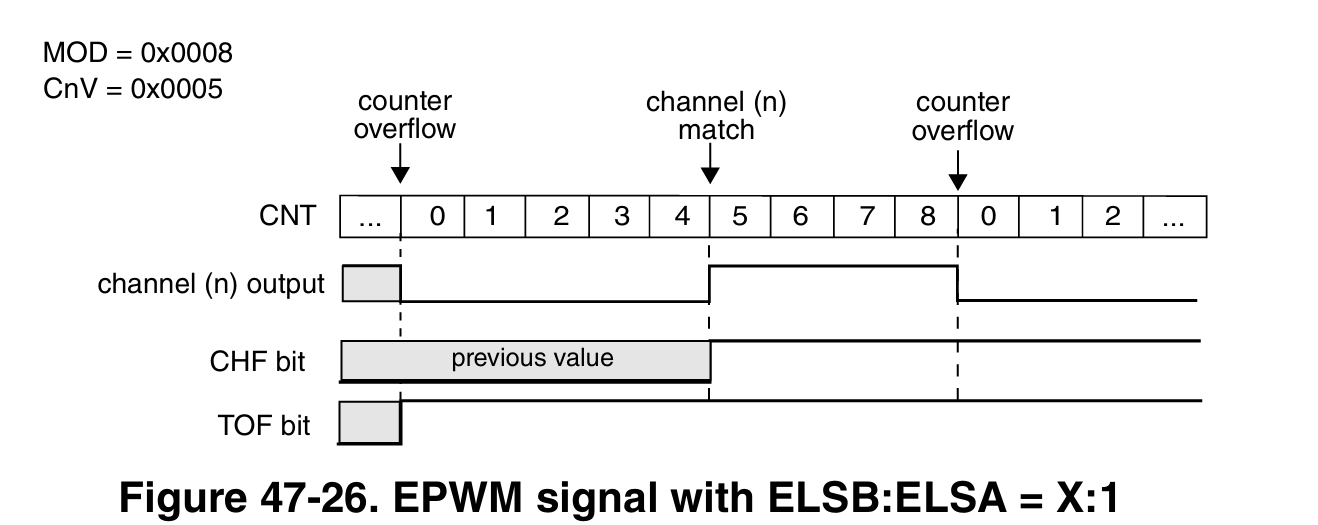

Counter Events

Counter events can be used as reload opportunities to FTM register synchronization

mechanism.

FTM Reload Points

- Up-Counter

- Up-down Counter

- Free running Counter

- Counter reset

- Counter event

FTM Channel Modes

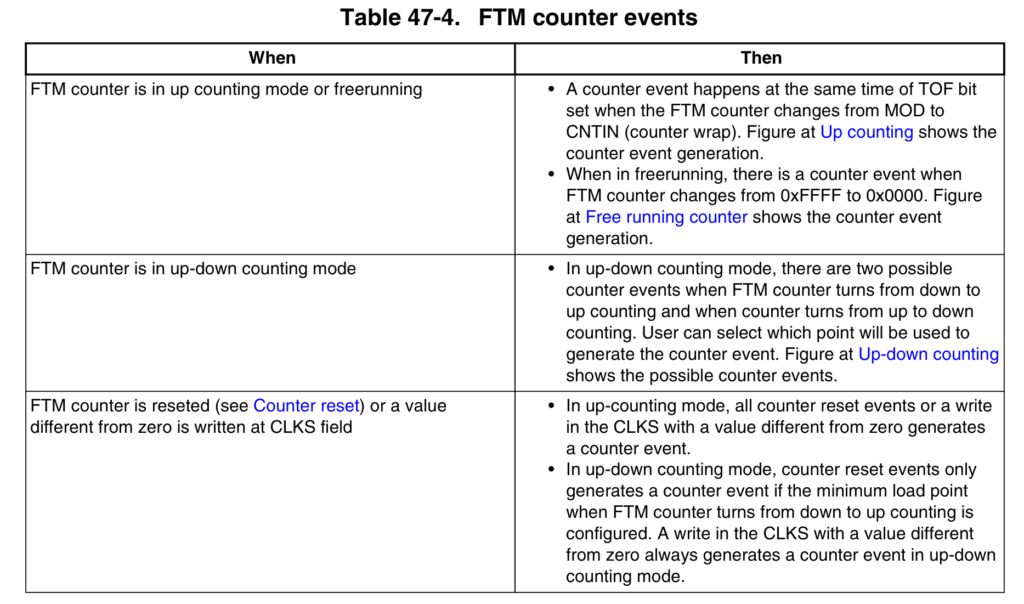

- FTM Input Capture Mode

–> When a selected edge occurs on the channel input, the current value of the FTM counter

is captured into the CnV register, at the same time the CHF bit is set and the channel

interrupt is generated if enabled by CHIE = 1.

Writes to the CnV register are ignored in input capture mode.

If the channel (n) is in input capture mode and CnSC[ICRST = 1], then when the selected

input capture event occurs in the channel (n) input signal, the current value of the FTM

counter is captured into the CnV register, the CHF bit is set, the channel (n) interrupt is

generated (if CHIE = 1) and the FTM counter is reset to the CNTIN register value.

This allows the FTM to measure a period/pulse being applied to the channel (n) input

(number of the FTM input clocks) without having to implement a subtraction calculation

in software subsequent to the event occurring.

- Capture Test Mode

- Dual Edge Capture Mode

- One-Shot Capture Mode

- Continous Capture Mode

- Pulse Width Measurment

- Period Measurment

- FTM Output Capture Mode

In Output Compare mode, the FTM can generate timed pulses with programmable

position, polarity, duration, and frequency. When the counter matches the value in the

CnV register of an output compare channel, the channel (n) output can be set, cleared, or

toggled.

When a channel is initially configured to Toggle mode, the previous value of the channel

output is held until the first output compare event occurs.

- Software Output Control

- Hardware Output control mode

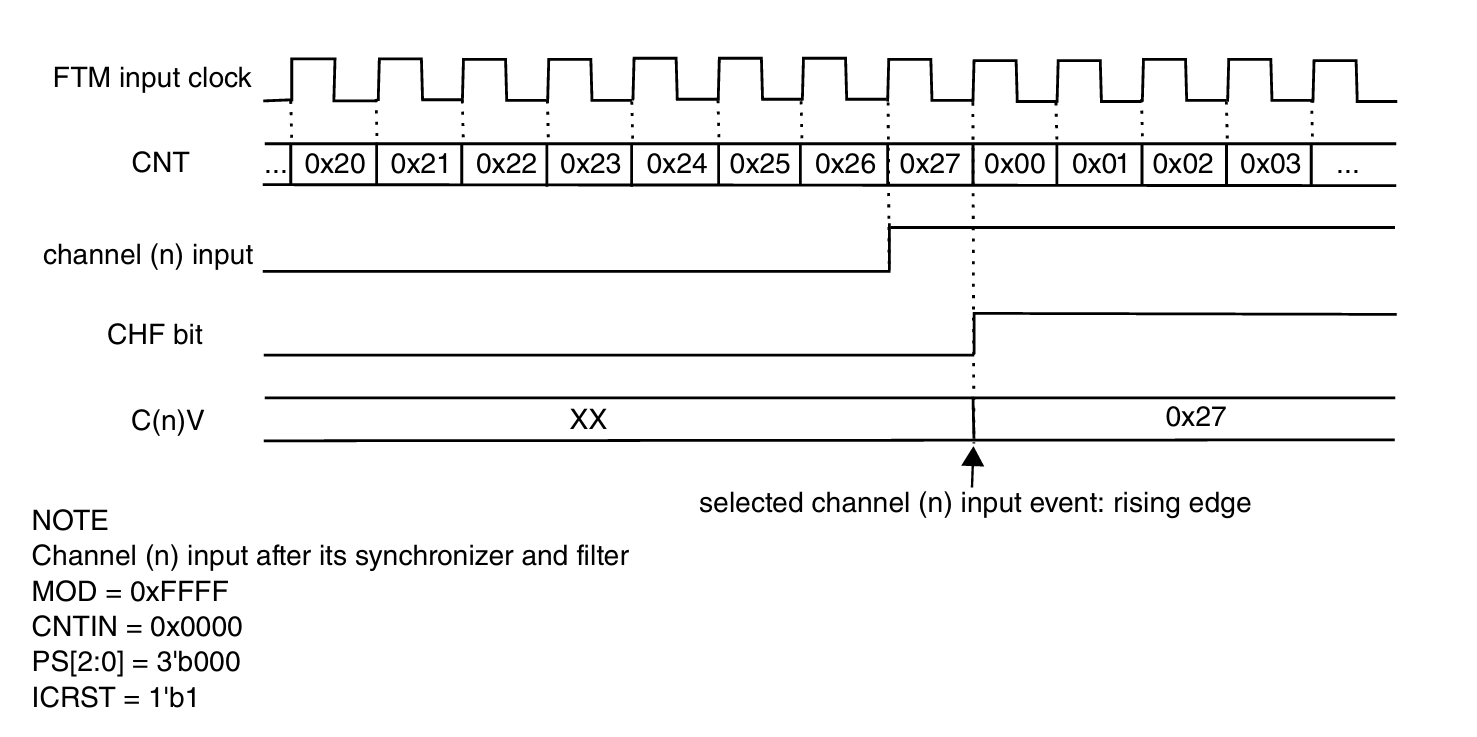

- FTM PWM Mode

- Edge Aligned PWM

This type of PWM signal is called edge-aligned that is Signals are generated with High and Low values repeatdely as counter reaches the set values in CnV and MOD register.

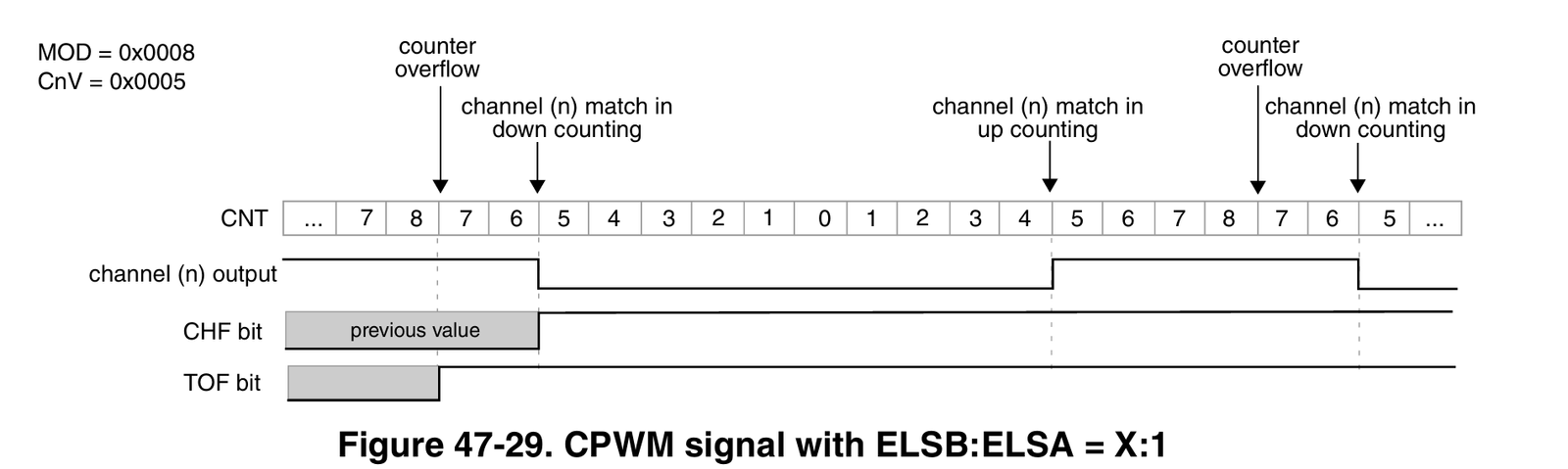

- Center Aligned PWM Mode

- In the CPWM mode, the FTM counter counts up until it reaches MOD and then counts

down until it reaches CNTIN and match. happened when FTM counter = CnV.

- Combine Mode

In Combine mode, an even channel (n) and adjacent odd channel (n+1) are combined to

generate a PWM signal in the channel (n) output.

The channel (n) CHF bit is set and its interrupt is generated, if channel (n) CHIE = 1, at

the channel (n) match (FTM counter = C(n)V). The channel (n+1) CHF bit is set and its

interrupt is generated, if channel (n+1) CHIE = 1, at the channel (n+1) match (FTM

counter = C(n+1) V).

In this Asymmetrical PWM Mode also comes.

- Modified Combine PWM Mode

The Modified Combine PWM mode is intended to support the generation of PWM

signals where the period is not modified while the signal is being generated, but the duty

cycle will be varied. In this mode, an even channel (n) and adjacent odd channel (n+1)

are combined to generate a PWM signal in the channel (n) output. Thus, the channel (n)

match edge is fixed, and the channel (n+1) match edge can be varied.

Complementary Mode

In Complementary mode, the channel (n+1) output is the inverse of the channel (n)

output.

The channel (n+1) output is the same as the channel (n) output when:

- channels (n) and (n+1) are on Combine Mode or Modified Combine PWM Mode

The channel (n+1) output is independent from channel (n) output when:

- channel (n) is on Output Compare Mode, EPWM or CPWM

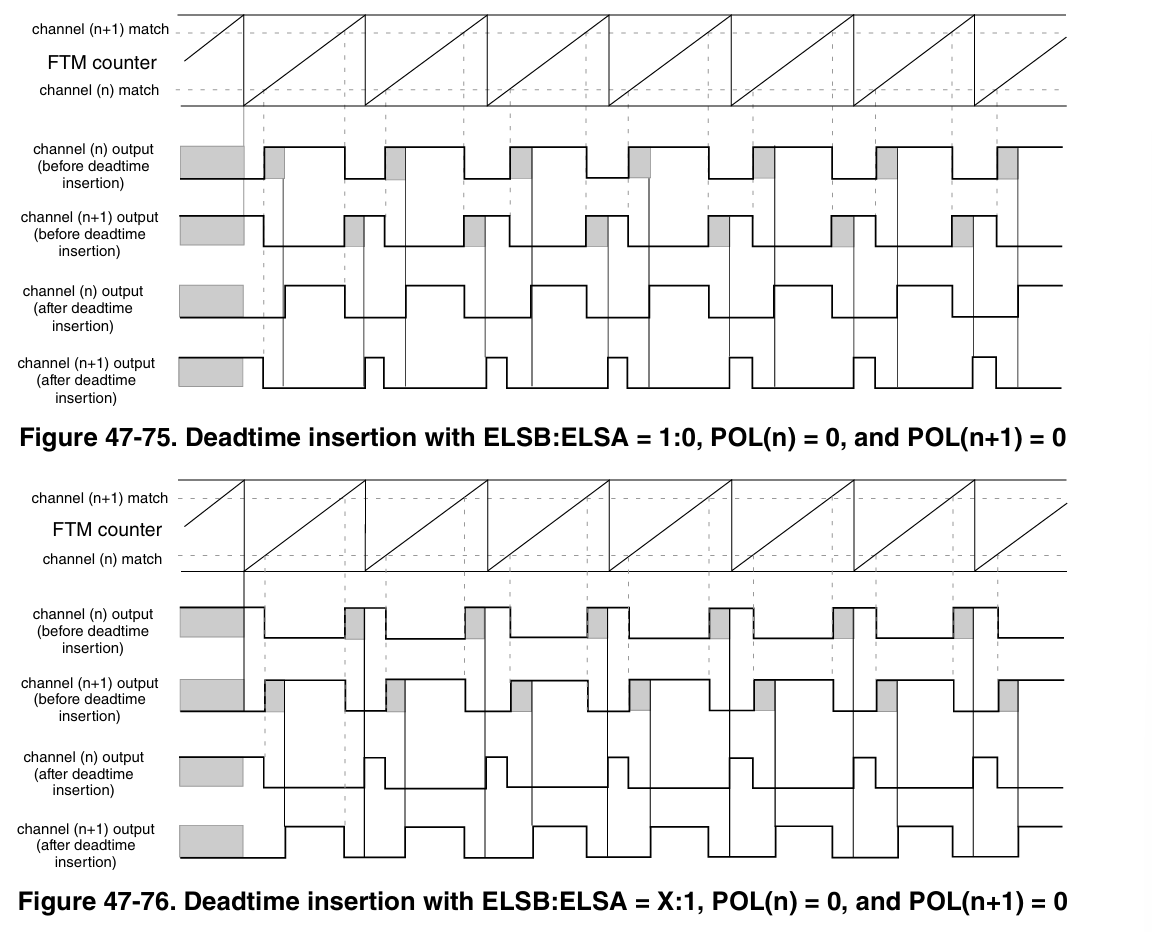

Deadtime insertion

DEADTIME register defines the deadtime delay that can be used for all FTM channels.

The clock for the DEADTIME delay is the FTM input clock divided by DTPS bits, and

the {DTVALEX[3:0], DTVAL[5:0]} bits define the deadtime modulo, that is, the

number of the deadtime prescaler clocks.

The deadtime delay insertion ensures that no two complementary signals (channels (n)

and (n+1)) drive the active state at the same time.

- If POL(n) = 0, POL(n+1) = 0, and the deadtime is enabled, then when the channel (n)

match (FTM counter = C(n)V) occurs, the channel (n) output remains at the low value

until the end of the deadtime delay when the channel (n) output is set. Similarly, when the

channel (n+1) match (FTM counter = C(n+1)V) occurs, the channel (n+1) output remains

at the low value until the end of the deadtime delay when the channel (n+1) output is set.

See the following figures. - If POL(n) = 1, POL(n+1) = 1, and the deadtime is enabled, then when the channel (n)

match (FTM counter = C(n)V) occurs, the channel (n) output remains at the high value

until the end of the deadtime delay when the channel (n) output is cleared. Similarly, when the channel (n+1) match (FTM counter = C(n+1)V) occurs, the channel (n+1)

output remains at the high value until the end of the deadtime delay when the channel (n

+1) output is cleared.

What is PWM Synchronization

Synchronization between PWM module and analog-to-digital

converter (ADC) is one of the key requirements in motor

control and power conversion applications. These applications

use pulse with modulation (PWM) to generate voltages or

currents in the system and thus a ripple can be observed when

system quantities are measured. The quantity ripple makes

analog-to-digital conversion difficult since actual value of

quantity corresponds to the moment of the ADC sampling.

This issue can be solved by PWM to ADC synchronization.

When the analog-to-digital conversion sample is taken just in

the middle of PWM pulse, the ADC result corresponds to

average value of the measured quantity.

FTM Polarity Control

FTM Fault Detection Inputs

- Fault Control

- Automatic Falut Clearing

- Manual Fault Clearing

FTM Hardware Trigger and Synchronization

- PWM Synchronization

- FTM Counter Synchronization

- External Trigger

- Init Trigger

FTM Interrupts

FTM DMA

FTM Hall Sensor Support

For 3 phase motor control sensor-ed applications the use of Hall sensors, generally 3

sensors placed 120 degrees apart around the rotor, are deployed to detect position and

speed. Each of the 3 sensors provides a pulse that applied to an input capture pin, can

then be analyzed and both speed and position can be deduced

FTM Quadrature Encoder/Decoder

FTM Modulation Implementation

FTM Global Time Base

FTM supports global timer base through the GTB feature. Any of the FTM module could

be used as the GTB_EN source. The global timer base only allows the FTM counters to

start their operation synchronously, it does not automatically provide continuous

synchronization of FTM counters, meaning that the FTM counters may lose

synchronization during misc FTM operation.

FTM Inverting

FTM DeadTime

FTM Dithering

Lorem ipsum dolor sit amet, consectetur adipiscing elit. Ut elit tellus, luctus nec ullamcorper mattis, pulvinar dapibus leo.

FTM PWM

FTM blocks knowledge:

Way of PWM Generation:

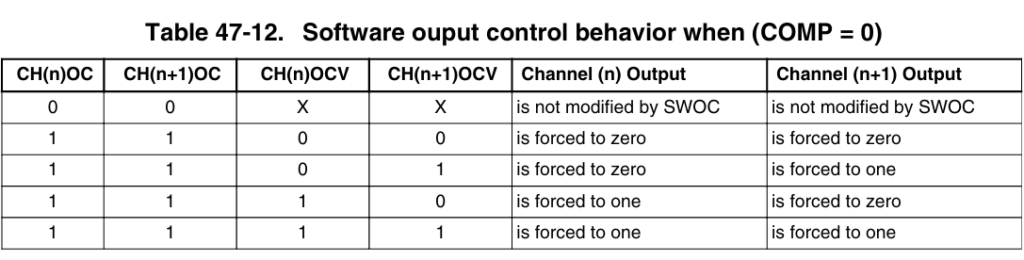

- Software Output Control Mode

- Hardware Output Control Mode

The software output control forces the channel output according to software defined

values at a specific time in the PWM generation. The CH(n)OC bit enables the software output control for a specific channel output and

the CH(n)OCV selects the value that is forced to this channel output.

- FTM Clock

- FTM Counter

- FTM deadtime/inverting dithering overview

- FTM Trigger

- FTM faults

- PWM configuration and maths concept